# Analog Engineer's Circuit Cookbook: Amplifiers

# **Second Edition**

SLYY137 - 03/2019

# Edited by:

Tim Green, Pete Semig and Collin Wells

Special thanks for technical contribution:

Tim Claycomb

Mamadou Diallo

Peter Iliya

Zak Kaye

Errol Leon

Marc Liu

Masashi Miyagawa

Gustaf Falk Olson

Bala Ravi

Takahiro Saito

Will Wang

# Analog Engineer's Circuit Cookbook: Amplifiers

(Second Edition)

# Message from the editors:

The Analog Engineer's Circuit Cookbook: Amplifiers provides amplifier sub-circuit ideas that can be quickly adapted to meet your specific system needs. Each circuit is presented as a "definition-by-example." They include step-by-step instructions, like a recipe, with formulas enabling you to adapt the circuit to meet your design goals. Additionally, all circuits are verified with SPICE simulations.

We've provided at least one recommended amplifier for each circuit, but you can swap it with another device if you've found one that's a better fit for your design. You can search our large portfolio of amplifiers at ti.com/amplifiers.

Our circuits require a basic understanding of amplifier concepts. If you're new to amplifier design, we highly recommend completing our TI Precision Labs (TIPL) training series. TIPL includes courses on introductory topics, such as device architecture, as well as advanced, application-specific problem-solving, using both theory and practical knowledge. Check out our curriculum for operational amplifiers (op amps), analog-to-digital converters (ADCs) and more at: ti.com/precisionlabs.

We hope you find this collection of amplifier circuits helpful in developing your designs. Our goal is to regularly update the cookbook with valuable amplifier circuit building blocks. You can check to see if your version is the latest at <a href="mailto:ti.com/circuitcookbooks">ti.com/circuitcookbooks</a>. If you have input on any of the existing circuits or would like to request additional amplifier cookbook circuits for the next edition please contact us at: <a href="mailto:opampcookbook@list.ti.com">opampcookbook@list.ti.com</a>.

#### Additional resources to explore

#### TI Precision Labs

#### ti.com/precisionlabs

- On-demand courses and tutorials ranging from introductory to advanced concepts that focus on application-specific problem solving

- Hands-on labs and evaluation modules (EVM) available

- TIPL Op Amps experimentation platform, ti.com/TIPL-amp-evm

- TIPL SAR ADC experimentation platform, ti.com/TIPL-Data Converters-evm

#### Analog Engineer's Pocket Reference

#### ti.com/analogrefguide

- PCB, analog and mixed-signal design formulae; includes conversions, tables and equations

- e-book, iTunes and Android apps and hardcopy available

## The Signal e-book

#### ti.com/signalbook

Op amp e-book with short, bite-sized lessons on design topics such as offset voltage, input bias current, stability, noise and more

#### TI Designs

#### ti.com/tidesigns

Ready-to-use reference designs with theory, calculations, simulations schematics, PCB files and bench test results

# TINA-TI™ Simulation Software

#### ti.com/tool/tina-ti

- Complete SPICE simulator for DC, AC, transient and noise analysis

- Includes schematic entry and post-processor for waveform math

#### Analog Engineer's Calculator

#### ti.com/analogcalc

ADC and amplifier design tools, noise and stability analysis, PCB and sensor tools

#### **Analog Wire Blog**

#### ti.com/analogwire

Technical blogs written by analog experts that include tips, tricks and design techniques

## TI E2E™ Community

#### ti.com/e2e

• Support forums for all TI products

#### Op Amp Circuit Quick Search and Parametric Search

#### ti.com/opamp-search

Search our operational amplifier portfolio by entering key parameters or by selecting a circuit function

## Op Amp Parametric Cross-Reference

#### ti.com/opampcrossreference

• Find similar TI Amplifiers using competitive part numbers

# DIY Amplifier Circuit Evaluation Module (DIYAMP-EVM) ti.com/DIYAMP-EVM

Single-channel circuit evaluation module providing SC70, SOT23 and SOIC package options in 12 popular amplifier configurations

# Dual-Channel DIY Amplifier Circuit Evaluation Module (DUAL-DIYAMP-EVM)

#### ti.com/dual-diyamp-evm

Dual-channel circuit evaluation module in an SOIC-8 package with 10 popular amplifier configurations

#### Want more circuits?

- Download the Analog Engineer's Circuit Cookbook for data converters

- Browse a complete list of amplifier

- and data converters circuits

Visit ti.com/circuitcookbooks

# **Table of Contents**

| Basic Circuits                                                                                    | Signal Conditioning                                                           |

|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Buffer (follower) circuit                                                                         | Single-ended input to differential output circuit138                          |

| Inverting amplifier circuit9                                                                      | Inverting op amp with inverting positive reference voltage circuit142         |

| Non-inverting amplifier circuit                                                                   | Non-inverting op amp with inverting positive reference voltage circuit146     |

| Inverting summer circuit                                                                          | Non-inverting op amp with non-inverting positive reference voltage            |

| Difference amplifier (subtractor) circuit                                                         | circuit150                                                                    |

| Two op amp instrumentation amplifier circuit                                                      | Inverting op amp with non-inverting positive reference voltage circuit.154    |

| Three op amp instrumentation amplifier circuit                                                    | Single-supply diff-in to diff-out AC amplifier circuit158                     |

| Integrator circuit                                                                                | Inverting dual-supply to single-supply amplifier circuit                      |

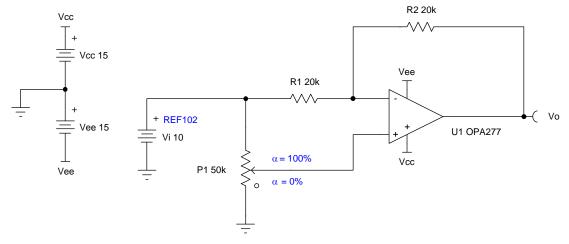

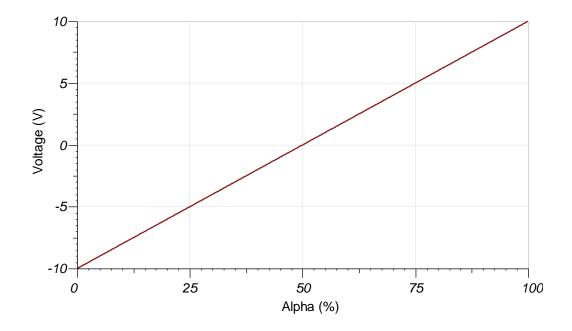

| Differentiator circuit                                                                            | Dual-supply, discrete, programmable gain amplifier circuit167                 |

| Command Camaina                                                                                   | AC coupled instrumentation amplifier circuit171                               |

| Current Sensing                                                                                   | Discrete wide bandwidth INA circuit175                                        |

| Transimpedance amplifier circuit                                                                  | Low-noise and long-range PIR sensor conditioner circuit179                    |

| Single-supply, low-side, unidirectional current-sensing solution with output swing to GND circuit | Temperature sensing with NTC circuit183                                       |

| Single-supply, low-side, unidirectional current-sensing circuit                                   | Temperature sensing with PTC circuit187                                       |

| Low-side, bidirectional current sensing circuit                                                   | Differential input to differential output circuit using a fully -differential |

| High-side, bidirectional current-sensing circuit with transient protection 63                     | amplifier191                                                                  |

| High-side current-sensing circuit design                                                          | Single-ended input to differential output circuit using a fully-differential  |

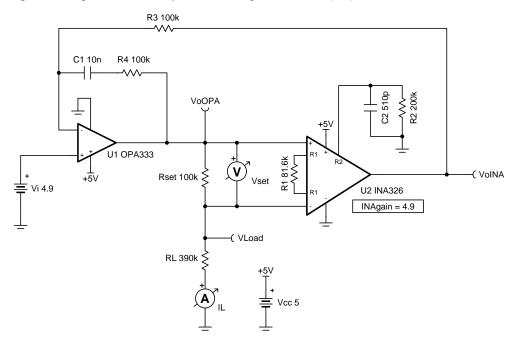

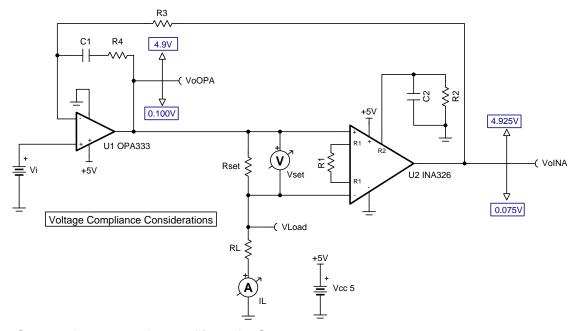

| 3-decade, load-current sensing circuit                                                            | amplifier197                                                                  |

| High-voltage, high-side floating current sensing circuit using current                            | Comparators                                                                   |

| output, current sense amplifier                                                                   | Signal and clock restoration circuit                                          |

| Low-drift, low-side, bidirectional current-sensing circuit with integrated                        | Comparator with and without hysteresis circuit                                |

| precision gain resistors81                                                                        | High-side current sensing with comparator circuit                             |

| Overcurrent event detection circuit                                                               | High-speed overcurrent detection circuit214                                   |

|                                                                                                   | Inverting comparator with hysteresis circuit                                  |

| Signal Sources                                                                                    | Low-power, bidirectional current sensing circuit                              |

| PWM generator circuit                                                                             | Non-inverting comparator with hysteresis circuit                              |

| Adjustable reference voltage circuit                                                              | Overvoltage protection with comparator circuit                                |

| Current Sources                                                                                   | Window comparator with integrated reference circuit                           |

| Low-level voltage-to-current converter circuit                                                    | Relaxation oscillator circuit                                                 |

|                                                                                                   | Thermal switch circuit                                                        |

| Filters                                                                                           | Undervoltage protection with comparator circuit                               |

| AC coupled (HPF) inverting amplifier circuit101                                                   | Window comparator circuit                                                     |

| AC coupled (HPF) non-inverting amplifier circuit105                                               | Zero crossing detection using comparator circuit                              |

| Band pass filtered inverting attenuator circuit109                                                |                                                                               |

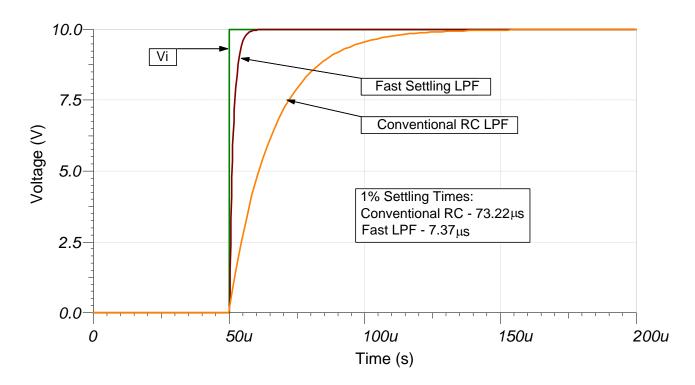

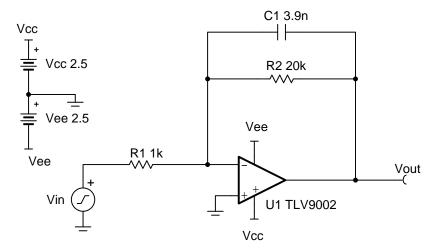

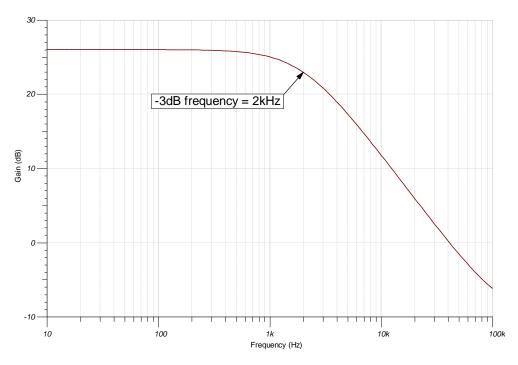

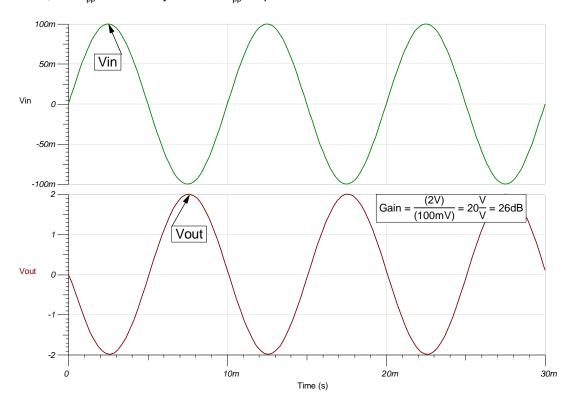

| Fast-settling low-pass filter circuit                                                             | Sensor Acquisition                                                            |

| Low-pass filtered, inverting amplifier circuit117                                                 | Single-supply strain gauge bridge amplifier circuit                           |

| Non-Linear Circuits (Rectifiers/Clamps/Peak Detectors)                                            | Photodiode amplifier circuit                                                  |

| Half-wave rectifier circuit                                                                       | Audio                                                                         |

| Full-wave rectifier circuit                                                                       | Non-inverting microphone pre-amplifier circuit                                |

| Single-supply, low-input voltage, full-wave rectifier circuit                                     |                                                                               |

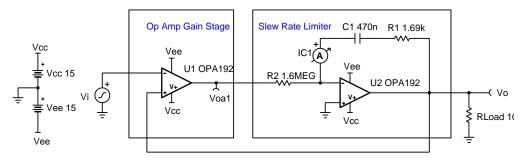

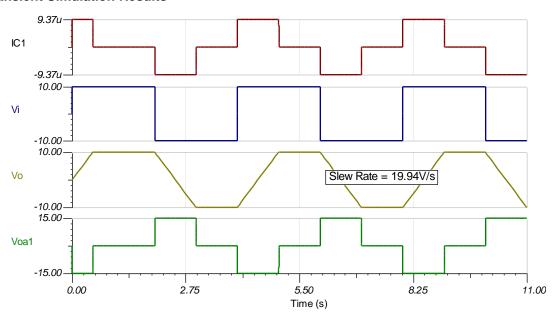

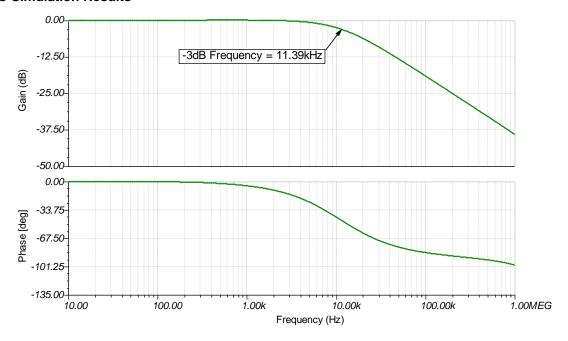

| Slaw rate limiter circuit                                                                         |                                                                               |

# SBOA269A-February 2018-Revised January 2019

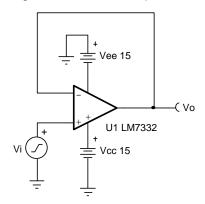

# Buffer (follower) circuit

# **Design Goals**

| Input      |            | Output     |            | Freq.  | Sup             | pply            |

|------------|------------|------------|------------|--------|-----------------|-----------------|

| $V_{iMin}$ | $V_{iMax}$ | $V_{oMin}$ | $V_{oMax}$ | f      | V <sub>cc</sub> | V <sub>ee</sub> |

| -10V       | 10V        | -10V       | 10V        | 100kHz | 15V             | -15V            |

#### **Design Description**

This design is used to buffer signals by presenting a high input impedance and a low output impedance. This circuit is commonly used to drive low-impedance loads, analog-to-digital converters (ADC) and buffer reference voltages. The output voltage of this circuit is equal to the input voltage.

- 1. Use the op-amp linear output operating range, which is usually specified under the A<sub>OL</sub> test conditions.

- 2. The small-signal bandwidth is determined by the unity-gain bandwidth of the amplifier.

- 3. Check the maximum output voltage swing versus frequency graph in the datasheet to minimize slewinduced distortion.

- 4. The common mode voltage is equal to the input signal.

- 5. Do not place capacitive loads directly on the output that are greater than the values recommended in the datasheet.

- 6. High output current amplifiers may be required if driving low impedance loads.

- 7. For more information on op-amp linear operating region, stability, slew-induced distortion, capacitive load drive, driving ADCs, and bandwidth, see the Design References section.

The transfer function for this circuit follows:

$$V_o = V_i$$

1. Verify that the amplifier can achieve the desired output swing using the supply voltages provided. Use the output swing stated in the A<sub>OL</sub> test conditions. The output swing range of the amplifier must be greater than the output swing required for the design.

$$-14V \le V_0 \le 14V$$

- The output swing of the LM7332 using ±15-V supplies is greater than the required output swing of the design. Therefore, this requirement is met.

- Review the Output Voltage versus Output Current curves in the product datasheet to verify the desired output voltage can be achieved for the desired output current.

- 2. Verify the input common mode voltage of the amplifier will not be violated using the supply voltage provided. The input common mode voltage range of the amplifier must be greater than the input signal voltage range.

$$-15.1 V \le V_{icm} \le 15.1 V$$

- The input common-mode range of the LM7332 using ±15-V supplies is greater than the required input common-mode range of the design. Therefore, this requirement is met.

- 3. Calculate the minimum slew rate required to minimize slew-induced distortion.

SR >

$$2 \times \pi \times Vp \times f = 2 \times \pi \times 10V \times 100kHz = 6.28V / \mu s$$

- The slew rate of the LM7332 is 15.2V/µs. Therefore, this requirement is met.

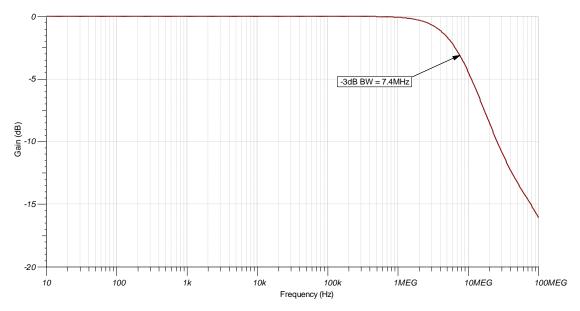

- 4. Verify the device will have sufficient bandwidth for the desired output signal frequency.

$$f_{\text{signal}} < f_{\text{unity}}$$

100*kHz* < 7.5*MHz*

The desired output signal frequency is less than the unity-gain bandwidth of the LM7332. Therefore, this requirement is met. www.ti.com

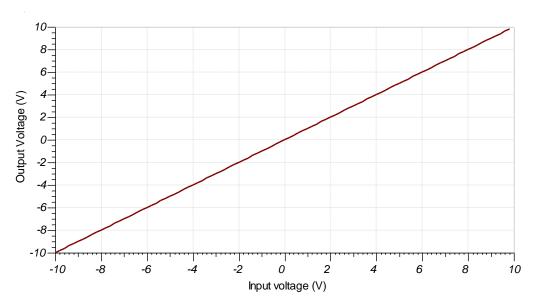

# **Design Simulations**

# **DC Simulation Results**

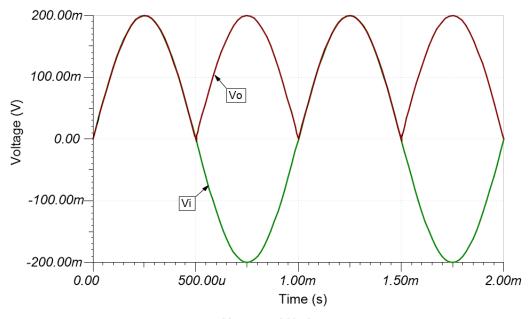

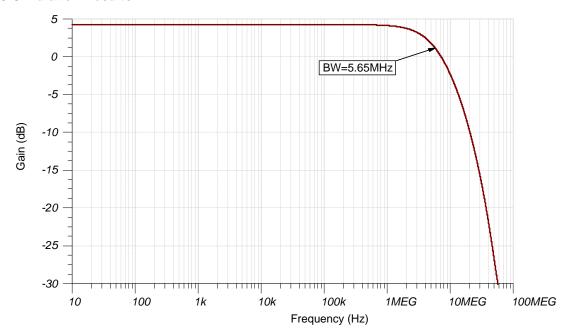

#### **AC Simulation Results**

# **Design References**

See the Analog Engineer's Circuit Cookbooks for TI's comprehensive circuit library.

For more information, see the Capacitive Load Drive Verified Reference Design Using an Isolation Resistor TI Design.

See the circuit SPICE simulation file SBOC491 - http://www.ti.com/lit/zip/sboc491.

For more information on many op amp topics including common-mode range, output swing, bandwidth, slew rate, and how to drive an ADC, see TI Precision Labs.

# **Design Featured Op Amp**

| LM7332                    |                      |  |  |

|---------------------------|----------------------|--|--|

| V <sub>ss</sub>           | 2.5V to 32V          |  |  |

| V <sub>inCM</sub>         | Rail-to-rail         |  |  |

| V <sub>out</sub>          | Rail-to-rail         |  |  |

| V <sub>os</sub>           | 1.6mV                |  |  |

| I <sub>q</sub>            | 2mA                  |  |  |

| I <sub>b</sub>            | 1µA                  |  |  |

| UGBW                      | 7.5MHz (±5-V supply) |  |  |

| SR                        | 15.2V/µs             |  |  |

| #Channels                 | 2                    |  |  |

| www.ti.com/product/LM7332 |                      |  |  |

# Design Alternate Op Amp

| OPA192            |                           |  |  |

|-------------------|---------------------------|--|--|

| V <sub>ss</sub>   | 4.5V to 36V               |  |  |

| V <sub>inCM</sub> | Rail-to-rail              |  |  |

| V <sub>out</sub>  | Rail-to-rail              |  |  |

| V <sub>os</sub>   | 5µV                       |  |  |

| I <sub>q</sub>    | 1mA                       |  |  |

| I <sub>b</sub>    | 5pA                       |  |  |

| UGBW              | 10MHz                     |  |  |

| SR                | 20V/µs                    |  |  |

| #Channels         | 1, 2, 4                   |  |  |

| www.ti.com/p      | www.ti.com/product/opa192 |  |  |

The following device is for battery-operated or power-conscious designs outside of the original design goals described earlier, where lowering the total system power is desired.

| LPV511            |                           |  |  |

|-------------------|---------------------------|--|--|

| V <sub>ss</sub>   | 2.7V to 12V               |  |  |

| V <sub>inCM</sub> | Rail-to-rail              |  |  |

| V <sub>out</sub>  | Rail-to-rail              |  |  |

| V <sub>os</sub>   | 0.2mV                     |  |  |

| I <sub>q</sub>    | 1.2µA                     |  |  |

| I <sub>b</sub>    | 0.8nA                     |  |  |

| UGBW              | 27KHz                     |  |  |

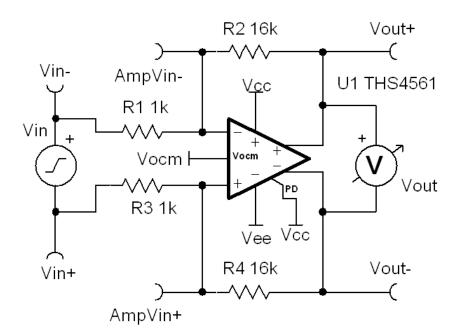

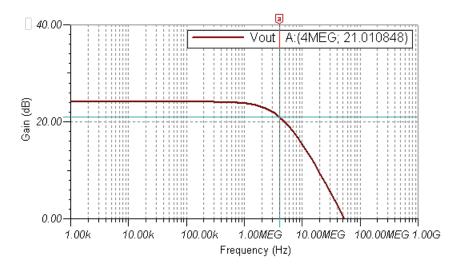

| SR                | 7.5V/ms                   |  |  |

| #Channels         | 1                         |  |  |

| www.ti.com/p      | www.ti.com/product/lpv511 |  |  |

# **Revision History**

| Revision | Date         | Change                                                                      |

|----------|--------------|-----------------------------------------------------------------------------|

| Α        | January 2019 | Downscale title. Added LPV511 table in the Design Alternate Op Amp section. |

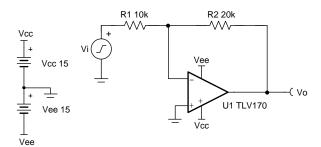

# Inverting amplifier circuit

#### **Design Goals**

| Input             |                   | Output            |                   | Freq. | Sup             | pply            |

|-------------------|-------------------|-------------------|-------------------|-------|-----------------|-----------------|

| V <sub>iMin</sub> | V <sub>iMax</sub> | V <sub>oMin</sub> | V <sub>oMax</sub> | f     | V <sub>cc</sub> | V <sub>ee</sub> |

| -7V               | 7V                | -14V              | 14V               | 3kHz  | 15V             | -15V            |

#### **Design Description**

This design inverts the input signal, V<sub>i</sub>, and applies a signal gain of -2V/V. The input signal typically comes from a low-impedance source because the input impedance of this circuit is determined by the input resistor, R<sub>1</sub>. The common-mode voltage of an inverting amplifier is equal to the voltage connected to the non-inverting node, which is ground in this design.

Copyright © 2018, Texas Instruments Incorporated

- 1. Use the op amp in a linear operating region. Linear output swing is usually specified under the A<sub>OI</sub> test conditions. The common-mode voltage in this circuit does not vary with input voltage.

- 2. The input impedance is determined by the input resistor. Make sure this value is large when compared to the source's output impedance.

- 3. Using high value resistors can degrade the phase margin of the circuit and introduce additional noise in the circuit.

- 4. Avoid placing capacitive loads directly on the output of the amplifier to minimize stability issues.

- 5. Small-signal bandwidth is determined by the noise gain (or non-inverting gain) and op amp gainbandwidth product (GBP). Additional filtering can be accomplished by adding a capacitor in parallel to R<sub>2</sub>. Adding a capacitor in parallel with R<sub>2</sub> will also improve stability of the circuit if high value resistors are used.

- 6. Large signal performance may be limited by slew rate. Therefore, check the maximum output swing versus frequency plot in the data sheet to minimize slew-induced distortion.

- 7. For more information on op amp linear operating region, stability, slew-induced distortion, capacitive load drive, driving ADCs, and bandwidth please see the Design References section.

The transfer function of this circuit is given below.

$$V_o = V_i \times \left(-\frac{R_2}{R_1}\right)$$

1. Determine the starting value of  $R_1$ . The relative size of  $R_1$  to the signal source's impedance affects the gain error. Assuming the signal source's impedance is low (for example,  $100\Omega$ ), set  $R_1$ = $10k\Omega$  for 1% gain error.

$$R_1 = 10k\Omega$$

2. Calculate the gain required for the circuit. Since this is an inverting amplifier use  $V_{iMin}$  and  $V_{oMax}$  for the calculation.

$$G = \frac{V_{oMax}}{V_{iMin}} = \frac{14V}{-7V} = -2\frac{V}{V}$$

3. Calculate R<sub>2</sub> for a desired signal gain of -2V/V.

$$G = {} - \frac{R_2}{R_1} \! \to R_2 \! = {} - G \textbf{ x } R_1 \! = {} - ({} - 2\frac{V}{V}) \textbf{ x } 10 k \Omega \! = 20 k \Omega$$

4. Calculate the small signal circuit bandwidth to ensure it meets the 3kHz requirement. Be sure to use the noise gain, or non-inverting gain, of the circuit.

$$\begin{split} GBP_{TLV170} &= 1.2 MHz & (\\ NG &= 1 + \frac{R_2}{R_1} = 3\frac{V}{V} \\ BW &= \frac{GBP}{NG} = \frac{1.2 MHz}{3V/V} = 400 kHz \end{split}$$

5. Calculate the minimum slew rate required to minimize slew-induced distortion.

$$\begin{split} V_p &= \frac{SR}{2 \times \pi \times f} \rightarrow SR > 2 \times \pi \times f \times V_p \\ SR &> 2 \times \pi \times 3 \text{kHz} \times 14 \text{V} = 263 \text{ . } 89 \frac{\text{kV}}{\text{s}} = 0 \text{ . } 26 \frac{\text{V}}{\text{us}} \end{split}$$

- SR<sub>TLV170</sub>=0.4V/µs, therefore it meets this requirement.

- 6. To avoid stability issues ensure that the zero created by the gain setting resistors and input capacitance of the device is greater than the bandwidth of the circuit.

$$\begin{split} \frac{1}{2 \times \pi \times (C_{cm} + C_{diff}) \times (R_2 \| R_1)} &> \frac{GBP}{NG} \\ \frac{1}{2 \times \pi \times 3pF + 3pF} \times \frac{20k\Omega \times 10k\Omega}{20k\Omega + 10k\Omega} &> \frac{1.2MHz}{3V/V} \\ 43.77MHz &> 400kHz \end{split}$$

- C<sub>cm</sub> and C<sub>diff</sub> are the common-mode and differential input capacitances of the TLV170, respectively.

- · Since the zero frequency is greater than the bandwidth of the circuit, this requirement is met.

# **Design Simulations**

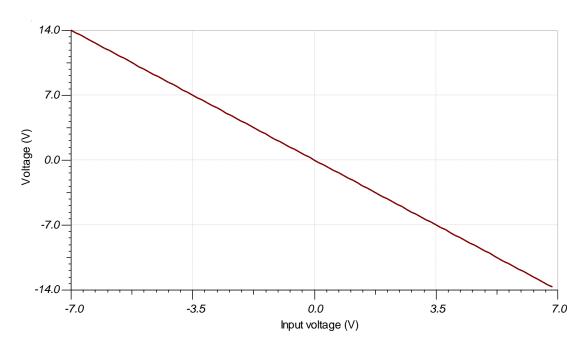

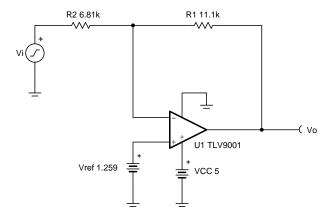

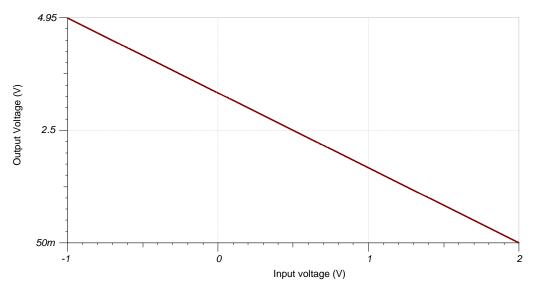

## **DC Simulation Results**

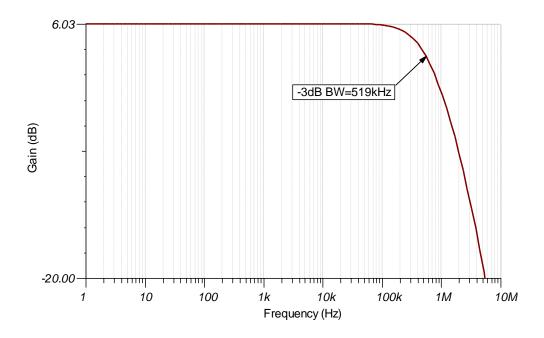

## **AC Simulation Results**

The bandwidth of the circuit depends on the noise gain, which is 3V/V. The bandwidth is determined by looking at the –3dB point, which is located at 3dB given a signal gain of 6dB. The simulation sufficiently correlates with the calculated value of 400kHz.

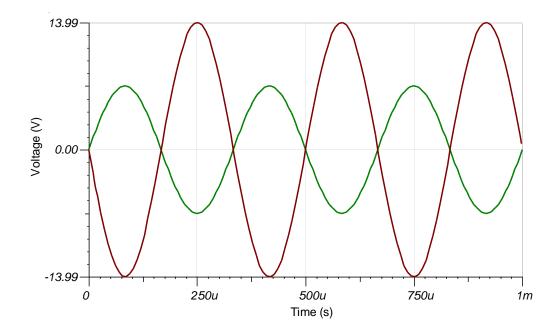

# **Transient Simulation Results**

The output is double the magnitude of the input, and inverted.

www.ti.com

# **Design References**

See Analog Engineer's Circuit Cookbooks for TI's comprehensive circuit library.

See circuit SPICE simulation file SBOC492.

For more information on many op amp topics including common-mode range, output swing, bandwidth, and how to drive an ADC please visit TI Precision Labs.

# **Design Featured Op Amp**

| TLV170                    |                        |  |  |

|---------------------------|------------------------|--|--|

| V <sub>ss</sub>           | ±18V (36V)             |  |  |

| V <sub>inCM</sub>         | (Vee-0.1V) to (Vcc-2V) |  |  |

| V <sub>out</sub>          | Rail-to-rail           |  |  |

| V <sub>os</sub>           | 0.5mV                  |  |  |

| I <sub>q</sub>            | 125µA                  |  |  |

| I <sub>b</sub>            | 10pA                   |  |  |

| UGBW                      | 1.2MHz                 |  |  |

| SR                        | 0.4V/µs                |  |  |

| #Channels 1, 2, 4         |                        |  |  |

| www.ti.com/product/tlv170 |                        |  |  |

# **Design Alternate Op Amp**

| LMV358                    |                                                    |  |

|---------------------------|----------------------------------------------------|--|

| V <sub>ss</sub>           | 2.7 to 5.5V                                        |  |

| V <sub>inCM</sub>         | (V <sub>ee</sub> -0.2V) to (V <sub>cc</sub> -0.8V) |  |

| V <sub>out</sub>          | Rail-to-rail                                       |  |

| V <sub>os</sub>           | 1.7mV                                              |  |

| I <sub>q</sub>            | 210μΑ                                              |  |

| l <sub>b</sub>            | 15nA                                               |  |

| UGBW                      | 1MHz                                               |  |

| SR                        | 1V/μs                                              |  |

| #Channels                 | 1 (LMV321), 2 (LMV358), 4<br>(LMV324)              |  |

| www.ti.com/product/lmv358 |                                                    |  |

# **Revision History**

| Revision | Date         | Change                                                        |

|----------|--------------|---------------------------------------------------------------|

| Α        | January 2019 | Downscale title. Added link to circuit cookbook landing page. |

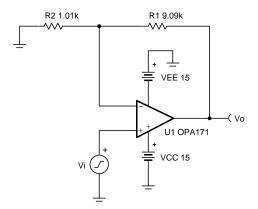

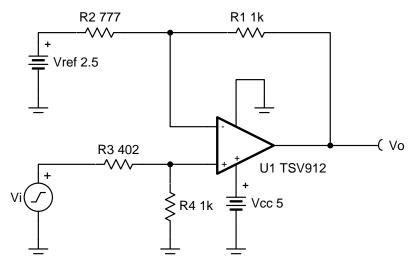

# Non-inverting amplifier circuit

#### **Design Goals**

| Input |       | Ou    | tput  | Supply |      |

|-------|-------|-------|-------|--------|------|

| ViMin | ViMax | VoMin | VoMax | Vcc    | Vee  |

| -1V   | 1V    | -10V  | 10    | 15V    | -15V |

#### **Design Description**

This design amplifies the input signal,  $V_i$ , with a signal gain of 10V/V. The input signal may come from a high-impedance source (for example,  $M\Omega$ ) because the input impedance of this circuit is determined by the extremely high input impedance of the op amp (for example,  $G\Omega$ ). The common-mode voltage of a non-inverting amplifier is equal to the input signal.

- Use the op amp linear output operating range, which is usually specified under the A<sub>OL</sub> test conditions. The common-mode voltage is equal to the input signal.

- 2. The input impedance of this circuit is equal to the input impedance of the amplifier.

- 3. Using high-value resistors can degrade the phase margin of the circuit and introduce additional noise in the circuit.

- 4. Avoid placing capacitive loads directly on the output of the amplifier to minimize stability issues.

- 5. The small-signal bandwidth of a non-inverting amplifier depends on the gain of the circuit and the gain bandwidth product (GBP) of the amplifier. Additional filtering can be accomplished by adding a capacitor in parallel to R<sub>1</sub>. Adding a capacitor in parallel with R<sub>1</sub> will also improve stability of the circuit if high-value resistors are used.

- 6. Large signal performance may be limited by slew rate. Therefore, check the maximum output swing versus frequency plot in the data sheet to minimize slew-induced distortion.

- 7. For more information on op amp linear operating region, stability, slew-induced distortion, capacitive load drive, driving ADCs, and bandwidth please see the Design References section.

The transfer function for this circuit is given below.

$$V_{o} = V_{i} \times (1 + \frac{R_{1}}{R_{2}})$$

1. Calculate the gain.

$$\begin{split} G &= \frac{V_{o\_max} - V_{o\_min}}{V_{i\_max} - V_{i\_min}} & (\\ G &= \frac{10V - -10V}{1\ V - -1\ V} = 10V\ /\ V \end{split}$$

2. Calculate values for R<sub>1</sub> and R<sub>2</sub>.

$$\begin{aligned} G &= 1 + \frac{R_1}{R_2} \\ &\text{Choose} \quad R_1 = 9 \ . \ 09k\Omega \\ &R_2 = \frac{R_1}{G-1} = \frac{9 \ . \ 09k\Omega}{10V/V-1} = 1 \ . \ 01k\Omega \end{aligned}$$

3. Calculate the minimum slew rate required to minimize slew-induced distortion.

SR

$$>$$

2 ×  $\pi$  ×  $V_p$  ×  $f$  = 2 ×  $\pi$  × 10V × 20kHz = 1 . 257V /  $\mu s$

- The slew rate of the OPA171 is 1.5V/µs, therefore it meets this requirement.

- 4. To maintain sufficient phase margin, ensure that the zero created by the gain setting resistors and input capacitance of the device is greater than the bandwidth of the circuit.

$$\frac{\frac{1}{2^{\times}\pi^{\times}(C_{cm}+C_{diff})^{\times}(R_{1}\|R_{2})}>\frac{GBP}{G}}{\frac{1}{2^{\times}\pi^{\times}}\frac{3pF+3pF}{1.0^{1}K\Omega^{\times}9.09K\Omega}}>\frac{3MHz}{10V/V}}{29.18MHz}>\frac{300kHz}{300kHz}$$

- C<sub>cm</sub> and C<sub>diff</sub> are the common-mode and differential input capacitances of the OPA171, respectively.

- · Since the zero frequency is greater than the bandwidth of the circuit, this requirement is met.

# **Design Simulations**

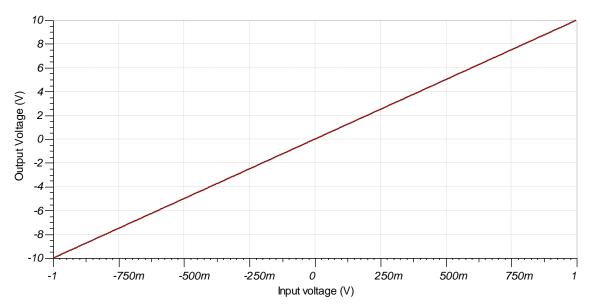

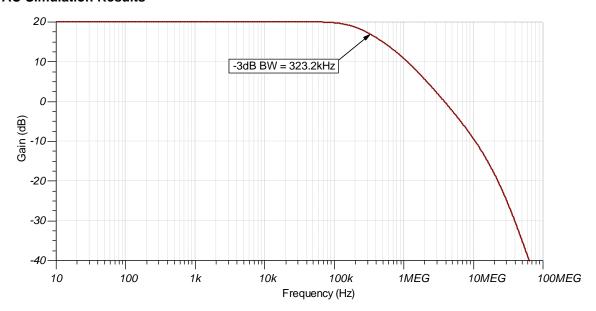

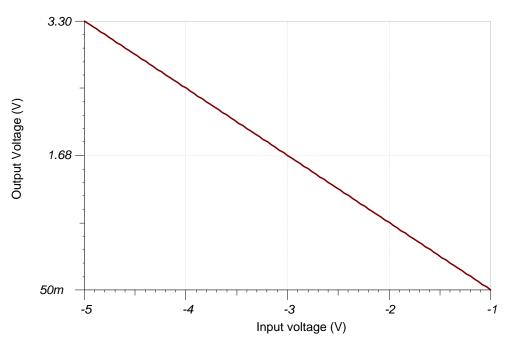

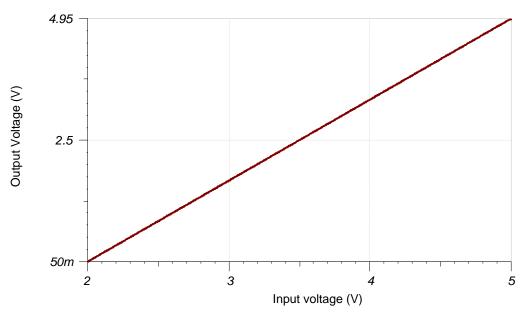

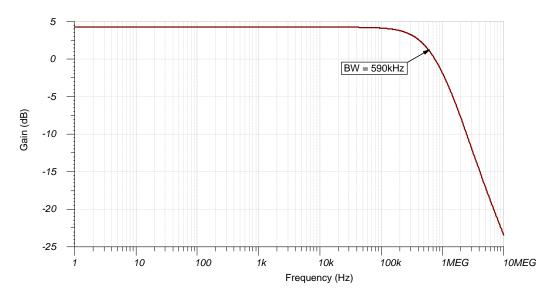

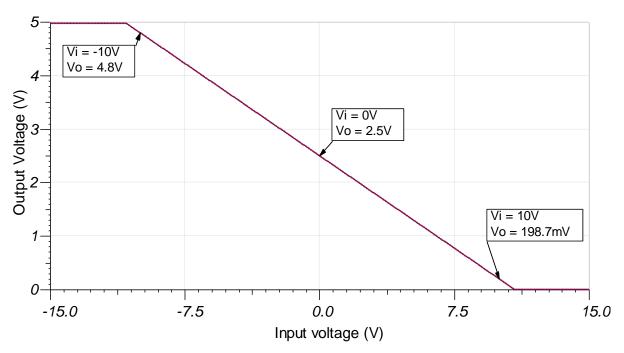

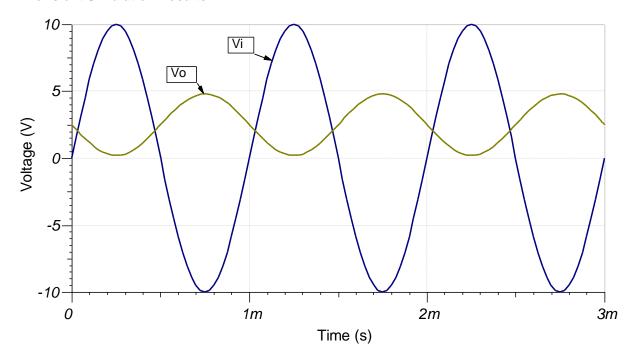

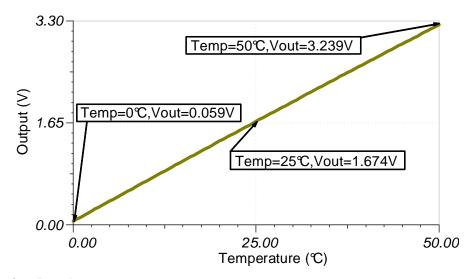

# **DC Simulation Results**

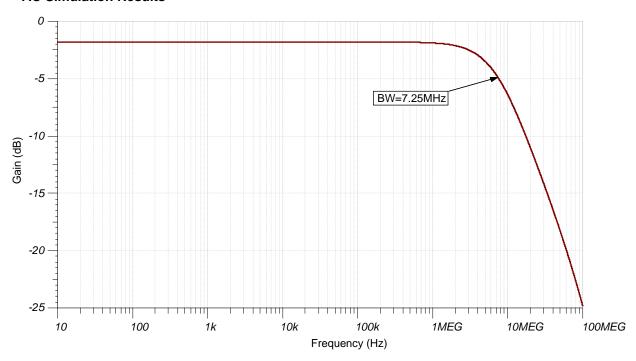

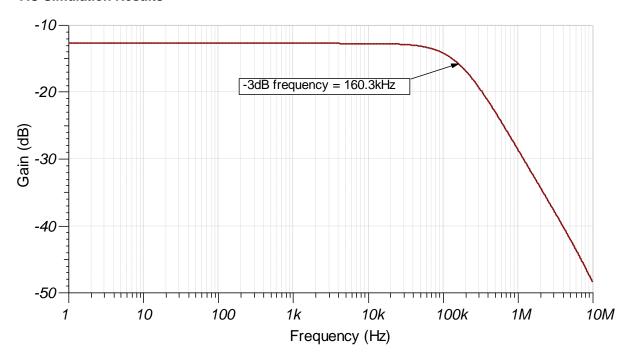

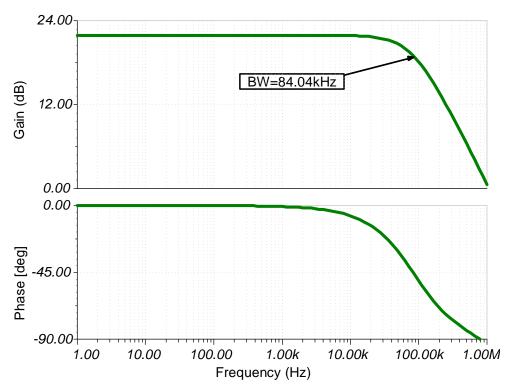

# **AC Simulation Results**

# **Design References**

See Analog Engineer's Circuit Cookbooks for TI's comprehensive circuit library.

See circuit SPICE simulation file SBOC493.

For more information on many op amp topics including common-mode range, output swing, and bandwidth please visit TI Precision Labs.

# **Design Featured Op Amp**

| OPA171                    |                                    |  |  |

|---------------------------|------------------------------------|--|--|

| $V_{ss}$                  | 2.7V to 36V                        |  |  |

| V <sub>inCM</sub>         | $(V_{ee}$ –0.1V) to $(V_{cc}$ –2V) |  |  |

| V <sub>out</sub>          | Rail-to-rail                       |  |  |

| V <sub>os</sub>           | 250µV                              |  |  |

| I <sub>q</sub>            | 475µA                              |  |  |

| I <sub>b</sub>            | 8pA                                |  |  |

| UGBW                      | 3MHz                               |  |  |

| SR                        | 1.5V/µs                            |  |  |

| #Channels                 | 1, 2, 4                            |  |  |

| www.ti.com/product/opa171 |                                    |  |  |

# **Design Alternate Op Amp**

| OPA191                    |              |  |  |  |

|---------------------------|--------------|--|--|--|

| V <sub>ss</sub>           | 4.5V to 36V  |  |  |  |

| V <sub>inCM</sub>         | Rail-to-rail |  |  |  |

| V <sub>out</sub>          | Rail-to-rail |  |  |  |

| V <sub>os</sub>           | 5μV          |  |  |  |

| I <sub>q</sub>            | 140µA        |  |  |  |

| I <sub>b</sub>            | 5pA          |  |  |  |

| UGBW                      | 2.5MHz       |  |  |  |

| SR                        | 7.5V/µs      |  |  |  |

| #Channels                 | 1, 2, 4      |  |  |  |

| www.ti.com/product/OPA191 |              |  |  |  |

# **Revision History**

| Revision | Date         | Change                                                                                                   |  |

|----------|--------------|----------------------------------------------------------------------------------------------------------|--|

| Α        | January 2019 | Downscale the title and changed title role to 'Amplifiers'. Added link to circuit cookbook landing page. |  |

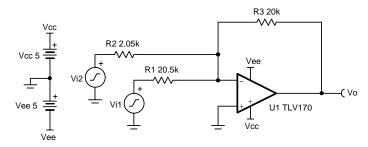

# Inverting summer circuit

## **Design Goals**

| Input 1     |             | Inp         | ut 2        | Output     |            | Freq. | Supply          |                 |

|-------------|-------------|-------------|-------------|------------|------------|-------|-----------------|-----------------|

| $V_{i1Min}$ | $V_{i1Max}$ | $V_{i2Min}$ | $V_{i2Max}$ | $V_{oMin}$ | $V_{oMax}$ | f     | V <sub>cc</sub> | V <sub>ee</sub> |

| –5V         | 5V          | –250mV      | 250mV       | -4.9V      | 4.9V       | 10kHz | 5V              | -5V             |

#### **Design Description**

This design sums (adds) and inverts two input signals,  $V_{i1}$  and  $V_{i2}$ . The input signals typically come from low-impedance sources because the input impedance of this circuit is determined by the input resistors,  $R_1$  and  $R_2$ . The common-mode voltage of an inverting amplifier is equal to the voltage connected to the non-inverting node, which is ground in this design.

Copyright © 2018, Texas Instruments Incorporated

- 1. Use the op amp in a linear operating region. Linear output swing is usually specified under the A<sub>OL</sub> test conditions. The common-mode voltage in this circuit does not vary with input voltage.

- 2. The input impedance is determined by the input resistors. Make sure these values are large when compared to the output impedance of the source.

- 3. Using high-value resistors can degrade the phase margin of the circuit and introduce additional noise in the circuit.

- 4. Avoid placing capacitive loads directly on the output of the amplifier to minimize stability issues.

- 5. Small-signal bandwidth is determined by the noise gain (or non-inverting gain) and op amp gain-bandwidth product (GBP). Additional filtering can be accomplished by adding a capacitor in parallel to R<sub>3</sub>. Adding a capacitor in parallel with R<sub>3</sub> will also improve stability of the circuit if high-value resistors are used.

- 6. Large signal performance may be limited by slew rate. Therefore, check the maximum output swing versus frequency plot in the data sheet to minimize slew-induced distortion.

- 7. For more information on op amp linear operating region, stability, slew-induced distortion, capacitive load drive, driving ADCs, and bandwidth please see the Design References section.

The transfer function for this circuit is given below.

$$V_{o} = V_{i \ 1} \times (-\frac{R_{3}}{R_{1}}) + V_{i \ 2} \times (-\frac{R_{3}}{R_{2}})$$

1. Select a reasonable resistance value for R<sub>3</sub>.

$$R_3 = 20k\Omega$$

2. Calculate gain required for  $V_{i1}$ . For this design, half of the output swing is devoted to each input.

$$G_{\text{Vi1}} \models \frac{\frac{V_{\text{oMax}} - V_{\text{oMin}}}{2}}{V_{\text{i 1 Max}} - V_{\text{i 1 Min}}} \models \frac{\frac{4.9V - (-4.9V)}{2}}{2.5V - (-2.5V)} \models 0.98\frac{V}{V} = -0.175 dB$$

3. Calculate the value of R<sub>1</sub>.

$$|G_{Vi1}| = \frac{R_3}{R_1} \rightarrow R_1 = \frac{R_3}{|G_{Vi1}|} = \frac{20k\Omega}{0.98V/V} = 20 . 4k\Omega \approx 20 . 5k\Omega \text{ (Standard Value)}$$

4. Calculate gain required for  $V_{i2}$ . For this design, half of the output swing is devoted to each input.

$$G_{\text{Vi2}} \models \frac{\frac{V_{\text{oMax}} - V_{\text{oMin}}}{2}}{V_{\text{i 2 Max}} - V_{\text{i 2 Min}}} \models \frac{\frac{4.9 \text{v} - (-4.9 \text{v})}{2}}{250 \text{mV} - (-250 \text{mV})} \models 9.8 \frac{\text{V}}{\text{V}} = 19.82 \text{dB}$$

5. Calculate the value of R<sub>2</sub>.

$$|\mathsf{G}_{\mathsf{VI2}}|=rac{\mathsf{R}_3}{\mathsf{R}_2} o \mathsf{R}_2=rac{\mathsf{R}_3}{|\mathsf{G}_{\mathsf{UP}}|}=rac{\mathsf{20k}\Omega}{\mathsf{9.8V/V}}=2$$

.  $\mathsf{04k}\Omega$  ≈  $2$  .  $\mathsf{05k}\Omega$  (Standard Value)

Calculate the small signal circuit bandwidth to ensure it meets the 10-kHz requirement. Be sure to use the noise gain (NG), or non-inverting gain, of the circuit. When calculating the noise gain note that R<sub>1</sub> and R<sub>2</sub> are in parallel.

$$\begin{split} GBP_{OPA170} &= 1.2 MHz & ( ) & ( ) \\ NG &= 1 + \frac{R_3}{R_1 \parallel R_2} = 1 + \frac{20 k \Omega}{1.86 k \Omega} = 11.75 \frac{V}{V} = 21.4 dB \\ BW &= \frac{GBP}{NG} = \frac{1.2 MHz}{11.75 V/V} = 102 kHz \end{split}$$

- This requirement is met because the closed-loop bandwidth is 102kHz and the design goal is 10kHz.

- 7. Calculate the minmum slew rate to minimize slew-induced distortion.

$$\begin{split} V_p &= \frac{SR}{2 \times \pi \times f} \rightarrow SR > 2 \times \pi \times f \times V_p \\ SR &> 2 \times \pi \times 10 \\ kHz \times 4.9 \\ V &= 307.87 \\ \frac{kV}{s} = 0.31 \\ \frac{V}{\mu s} \end{split}$$

- SR<sub>OPA170</sub>=0.4V/µs, therefore it meets this requirement.

- 8. To avoid stability issues ensure that the zero created by the gain setting resistors and input capacitance of the device is greater than the bandwidth of the circuit.

$$\frac{1}{2 \times \pi \times (C_{cm} + C_{diff}) \times (R_1 \| R_2 \| R_3)} > \frac{GBP}{NG}$$

$$\frac{1}{2 \times \pi \times 3pF + 3pF \times 1.7k\Omega} > \frac{1.2MHz}{11.75V/V}$$

$$15.6MHz > 102kHz$$

- C<sub>cm</sub> and C<sub>diff</sub> are the common-mode and differential input capacitances.

- · Since the zero frequency is greater than the bandwidth of the circuit, this requirement is met.

# **Design Simulations**

#### **DC Simulation Results**

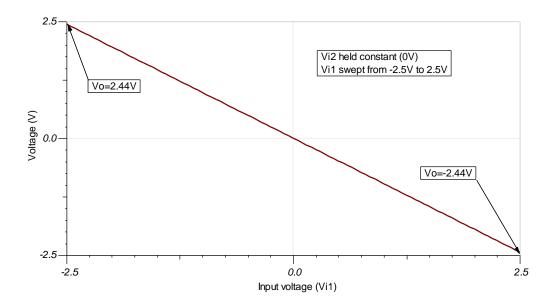

This simulation sweeps  $V_{i1}$  from -2.5V to 2.5V while  $V_{i2}$  is held constant at 0V. The output is inverted and ranges from -2.44V to 2.44V.

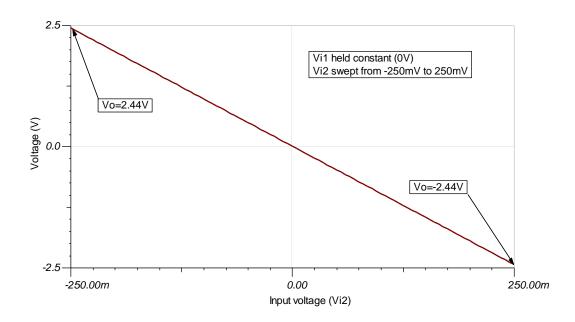

This simulation sweeps  $V_{i2}$  from -250 mV to 250 mV while  $V_{i1}$  is held constant at 0V. The output is inverted and ranges from -2.44 V to 2.44 V.

#### **AC Simulation Results**

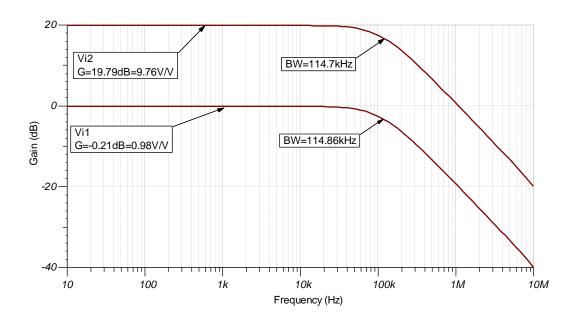

This simulation shows the bandwidth of the circuit. Note that the bandwidth is the same for either input. This is because the bandwidth depends on the noise gain of the circuit, not the signal gain of each input. These results correlate well with the calculations.

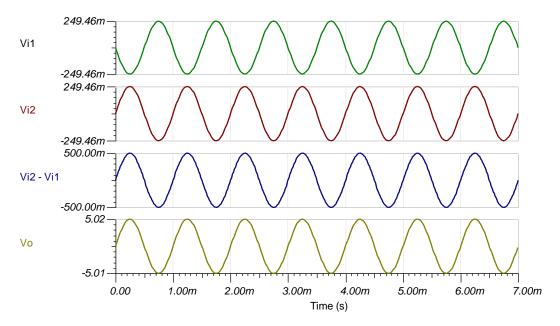

# **Transient Simulation Results**

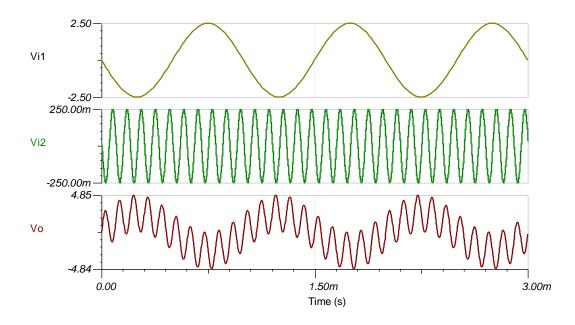

This simulation shows the inversion and summing of the two input signals.  $V_{i1}$  is a 1-kHz, 5- $V_{pp}$  sine wave and  $V_{i2}$  is a 10-kHz, 500-mV<sub>pp</sub> sine wave. Since both inputs are properly amplified or attenuated, the output is within specification.

www.ti.com

# **Design References**

See Analog Engineer's Circuit Cookbooks for TI's comprehensive circuit library.

See circuit SPICE simulation file SBOC494.

For more information on many op amp topics including common-mode range, output swing, bandwidth, and how to drive an ADC please visit TI Precision Labs.

# **Design Featured Op Amp**

| OPA170                    |                        |  |  |  |

|---------------------------|------------------------|--|--|--|

| V <sub>ss</sub>           | 2.7V to 36V            |  |  |  |

| V <sub>inCM</sub>         | (Vee-0.1V) to (Vcc-2V) |  |  |  |

| V <sub>out</sub>          | Rail-to-rail           |  |  |  |

| V <sub>os</sub>           | 0.25mV                 |  |  |  |

| I <sub>q</sub>            | 110µA                  |  |  |  |

| I <sub>b</sub>            | 8pA                    |  |  |  |

| UGBW                      | 1.2MHz                 |  |  |  |

| SR                        | 0.4V/µs                |  |  |  |

| #Channels 1, 2, 4         |                        |  |  |  |

| www.ti.com/product/opa170 |                        |  |  |  |

# **Design Alternate Op Amp**

| LMC7101                    |               |  |  |  |

|----------------------------|---------------|--|--|--|

| V <sub>ss</sub>            | 2.7V to 15.5V |  |  |  |

| V <sub>inCM</sub>          | Rail-to-rail  |  |  |  |

| V <sub>out</sub>           | Rail-to-rail  |  |  |  |

| V <sub>os</sub>            | 110µV         |  |  |  |

| I <sub>q</sub>             | 0.8mA         |  |  |  |

| I <sub>b</sub>             | 1pA           |  |  |  |

| UGBW                       | 1.1MHz        |  |  |  |

| SR                         | 1.1V/µs       |  |  |  |

| #Channels                  | 1             |  |  |  |

| www.ti.com/product/lmc7101 |               |  |  |  |

# **Revision History**

| Revision | Date         | Change                                                                                            |  |

|----------|--------------|---------------------------------------------------------------------------------------------------|--|

| Α        | January 2019 | Downscale title. Updated title role to 'Amplifiers'. Added link to circuit cookbook landing page. |  |

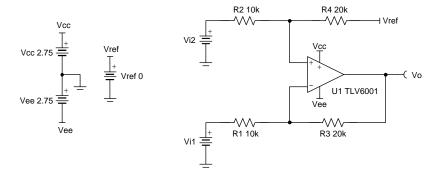

# Difference amplifier (subtractor) circuit

#### **Design Goals**

| Input (V <sub>i2</sub> -V <sub>i1</sub> ) |                | Out        | put               | CMRR (min) |                 | Supply   |           |

|-------------------------------------------|----------------|------------|-------------------|------------|-----------------|----------|-----------|

| $V_{idiffMin}$                            | $V_{idiffMax}$ | $V_{oMin}$ | V <sub>oMax</sub> | dB         | V <sub>cc</sub> | $V_{ee}$ | $V_{ref}$ |

| -1.25V                                    | 1.25V          | -2.5V      | 2.5V              | 50         | 2.75V           | -2.75V   | 0V        |

#### **Design Description**

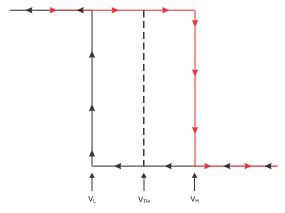

This design inputs two signals,  $V_{i1}$  and  $V_{i2}$ , and outputs their difference (subtracts). The input signals typically come from low-impedance sources because the input impedance of this circuit is determined by the resistive network. Difference amplifiers are typically used to amplify differential input signals and reject common-mode voltages. A common-mode voltage is the voltage common to both inputs. The effectiveness of the ability of a difference amplifier to reject a common-mode signal is known as common-mode rejection ratio (CMRR). The CMRR of a difference amplifier is dominated by the tolerance of the resistors.

Copyright © 2018, Texas Instruments Incorporated

- Use the op amp in a linear operating region. Ensure that the inputs of the op amp do not exceed the common-mode range of the device. Linear output swing is usually specified under the A<sub>OL</sub> test conditions.

- 2. The input impedance is determined by the input resistive network. Make sure these values are large when compared to the output impedance of the sources.

- 3. Using high-value resistors can degrade the phase margin of the circuit and introduce additional noise in the circuit.

- 4. Avoid placing capacitive loads directly on the output of the amplifier to minimize stability issues.

- 5. Small-signal bandwidth is determined by the noise gain (or non-inverting gain) and op amp gain-bandwidth product (GBP). Additional filtering can be accomplished by adding a capacitors in parallel to R<sub>3</sub> and R<sub>4</sub>. Adding capacitors in parallel with R<sub>3</sub> and R<sub>4</sub> will also improve stability of the circuit if high-value resistors are used.

- 6. Large signal performance may be limited by slew rate. Therefore, check the maximum output swing versus frequency plot in the data sheet to minimize slew-induced distortion.

- 7. For more information on op amp linear operating region, stability, slew-induced distortion, capacitive load drive, driving ADCs, and bandwidth please see the Design References section.

The complete transfer function for this circuit is shown below.

$$V_{o} = V_{i\,1} \times ({} - \frac{R_3}{R_1}) + V_{i\,2} \times (\frac{R_4}{R_2 + R_4}) \times (1 + \frac{R_3}{R_1}) + \text{Vref} \times (\frac{R_2}{R_2 + R_4}) \times (1 + \frac{R_3}{R_1})$$

If  $R_1 = R_2$  and  $R_3 = R_4$  the transfer function for this circuit simplifies to the following equation.

$$V_{o} = (V_{i 2} - V_{i 1}) \times \frac{R_{3}}{R_{1}} + Vref$$

- Where the gain, G, is R₃/R₁.

- 1. Determine the starting value of R<sub>1</sub> and R<sub>2</sub>. The relative size of R<sub>1</sub> and R<sub>2</sub> to the signal impedance of the source affects the gain error.

$$R_1 = R_2 = 10k\Omega$$

2. Calculate the gain required for the circuit.

$$G = \frac{V_{oMax} - V_{oMin}}{V_{idiffMax} - V_{idiffMin}} = \frac{2.5V - (-2.5V)}{1.25V - (-1.25V)} = 2\frac{V}{V} = 6 \text{ . } 02dB$$

3. Calculate the values for R<sub>3</sub> and R<sub>4</sub>.

$$G=2\frac{V}{V}=\frac{R_3}{R_1} \rightarrow 2 \times R_1=R_3=R_4=20 k\Omega$$

4. Calculate resistor tolerance to meet the minimum common-mode rejection ratio (CMRR). For minimum (worst-case) CMRR,  $\alpha$  = 4. For a more probable, or typical value of CMRR,  $\alpha$  = 0.33.

$$\begin{split} \text{CMRR}_{\text{dB}} &\cong 20 \text{log} 10 (\frac{1+G}{\alpha \times \epsilon}) \\ \epsilon &= \frac{1+G}{\alpha \times 10^{-\frac{CMRR_{\text{dB}}}{20}}} = \frac{3}{4 \times 10^{-\frac{50}{20}}} = 0 \ . \ 024 = 0 \ . \ 24\% \rightarrow \text{Use} \quad 0 \ . \ 1 \quad \% \quad \text{resistors} \end{split}$$

5. For quick reference, the following table compares resistor tolerance to minimum and typical CMRR values assuming G = 1 or G = 2. As shown above, as gain increases so does CMRR.

| Tolerance    | G=1 Minimum (dB) | G=1 Typical (dB) | G=2 Minimum (dB) | G=2 Typical (dB) |  |

|--------------|------------------|------------------|------------------|------------------|--|

| 0.01%=0.0001 | 0.01%=0.0001 74  |                  | 77.5             | 99.2             |  |

| 0.1%=0.001   | 54               | 75.6             | 57.5             | 79.2             |  |

| 0.5%=0.005   | 40               | 61.6             | 43.5             | 65.2             |  |

| 1%=0.01      | 34               | 55.6             | 37.5             | 59.2             |  |

| 5%=0.05      | 20               | 41.6             | 23.5             | 45.2             |  |

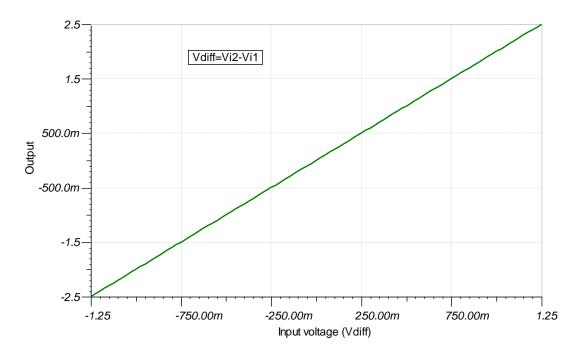

# **Design Simulations**

## **DC Simulation Results**

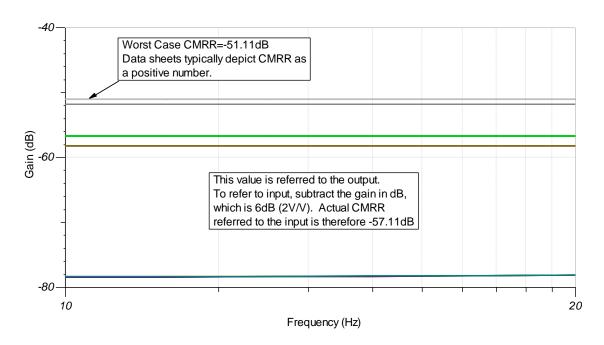

# **CMRR Simulation Results**

# **Design References**

See Analog Engineer's Circuit Cookbooks for TI's comprehensive circuit library.

See circuit SPICE simulation file SBOC495.

For more information on many op amp topics including common-mode range, output swing, bandwidth, and how to drive an ADC please visit TI Precision Labs. For more information on difference amplifier CMRR, please read Overlooking the obvious: the input impedance of a difference amplifier.

# **Design Featured Op Amp**

| TLV6001                    |              |  |  |  |

|----------------------------|--------------|--|--|--|

| V <sub>ss</sub>            | 1.8V to 5.5V |  |  |  |

| V <sub>inCM</sub>          | Rail-to-rail |  |  |  |

| V <sub>out</sub>           | Rail-to-rail |  |  |  |

| V <sub>os</sub>            | 750µV        |  |  |  |

| l <sub>q</sub>             | 75µA         |  |  |  |

| I <sub>b</sub>             | 1pA          |  |  |  |

| UGBW                       | 1MHz         |  |  |  |

| SR                         | 0.5V/µs      |  |  |  |

| #Channels 1, 2, 4          |              |  |  |  |

| www.ti.com/product/tlv6001 |              |  |  |  |

# **Design Alternate Op Amp**

| OPA320                    |              |  |  |  |

|---------------------------|--------------|--|--|--|

| V <sub>ss</sub>           | 1.8V to 5.5V |  |  |  |

| V <sub>inCM</sub>         | Rail-to-rail |  |  |  |

| V <sub>out</sub>          | Rail-to-rail |  |  |  |

| V <sub>os</sub>           | 40μV         |  |  |  |

| l <sub>q</sub>            | 1.5mA        |  |  |  |

| l <sub>b</sub>            | 0.2pA        |  |  |  |

| UGBW                      | 20MHz        |  |  |  |

| SR                        | 10V/µs       |  |  |  |

| #Channels                 | 1, 2         |  |  |  |

| www.ti.com/product/opa320 |              |  |  |  |

# **Revision History**

| Revision | Date         | Change                                                        |

|----------|--------------|---------------------------------------------------------------|

| А        | January 2019 | Downscale title. Added link to circuit cookbook landing page. |

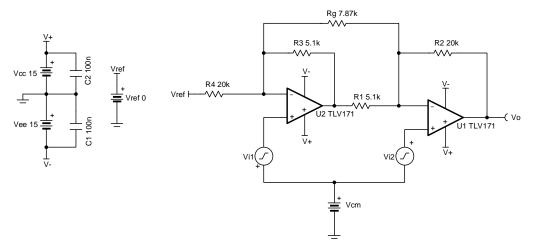

SBOA281-December 2018

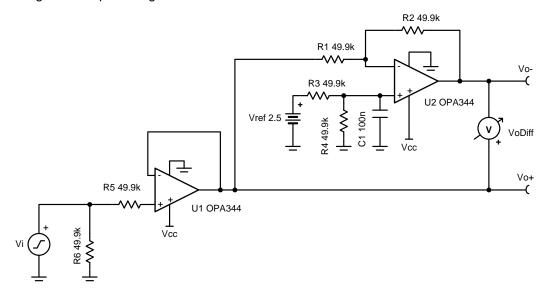

# Two op amp instrumentation amplifier circuit

#### **Design Goals**

| Input V <sub>iDiff</sub> (V <sub>i2</sub> - V <sub>i1</sub> ) |                  | Output            |                   | Supply          |                 |           |

|---------------------------------------------------------------|------------------|-------------------|-------------------|-----------------|-----------------|-----------|

| $V_{iDiff\_Min}$                                              | $V_{iDiff\_Max}$ | V <sub>oMin</sub> | V <sub>oMax</sub> | V <sub>cc</sub> | V <sub>ee</sub> | $V_{ref}$ |

| +/-1V                                                         | +/-2V            | -10V              | +10V              | 15V             | -15V            | 0V        |

| V <sub>cm</sub> | Gain Range    |  |  |

|-----------------|---------------|--|--|

| +/-10V          | 5V/V to 10V/V |  |  |

#### **Design Description**

This design amplifiers the difference between  $V_{i1}$  and  $V_{i2}$  and outputs a single ended signal while rejecting the common–mode voltage. Linear operation of an instrumentation amplifier depends upon the linear operation of its primary building block: op amps. An op amp operates linearly when the input and output signals are within the device's input common–mode and output–swing ranges, respectively. The supply voltages used to power the op amps define these ranges.

- 1. R<sub>a</sub> sets the gain of the circuit.

- High-value resistors can degrade the phase margin of the circuit and introduce additional noise in the circuit.

- 3. The ratio of  $R_4$  and  $R_3$  set the minimum gain when  $R_q$  is removed.

- 4. Ratios of  $R_2/R_1$  and  $R_4/R_3$  must be matched to avoid degrading the instrumentation amplifier's DC CMRR and ensuring the  $V_{ref}$  gain is 1V/V.

- 5. Linear operation is contingent upon the input common—mode and the output swing ranges of the discrete op amps used. The linear output swing ranges are specified under the A<sub>ol</sub> test conditions in the op amps datasheets.

1. Transfer function of this circuit.

$$V_{o} = V_{iDiff} \times G + V_{ref} = (V_{i2} - V_{i1}) \times G + V_{ref}$$

when  $V_{ref} = 0$ , the transfer function simplifies to the following equation:

$$V_o = (V_{i2} - V_{i1}) \times G$$

where G is the gain of the instrumentation amplifier and  $G = 1 + \frac{R_4}{R_3} + \frac{2R_2}{R_3}$

2. Select R<sub>4</sub> and R<sub>3</sub> to set the minimum gain.

$$\begin{split} G_{min} &= 1 + \frac{R_4}{R_3} = 5\frac{V}{V} \\ &\text{Choose} \quad R_4 = 20 k\Omega \\ G_{min} &= 1 + \frac{20 k\Omega}{R_3} = 5\frac{V}{V} \\ R_3 &= \frac{R_4}{5-1} = \frac{20 k\Omega}{4} = 5 k\Omega \rightarrow R_3 = 5 \text{ . } 1 k\Omega \quad \text{(Standard Value)} \end{split}$$

3. Select  $R_1$  and  $R_2$ . Ensure that  $R_1/R_2$  and  $R_3/R_4$  ratios are matched to set the gain applied to the reference voltage at 1V/V.

$$\begin{array}{l} \frac{V_{o\_ref}}{Vref} = (-\frac{R_3}{R_4}) \times (-\frac{R_2}{R_1}) = \frac{R_3 \times R_2}{R_4 \times R_1} = 1 \frac{V}{V} \\ \frac{R_2}{R_1} = \frac{R_4}{R_3} \to R_1 = R_3 = 5 \ . \ 1k\Omega \ \text{and} \ R_2 = R_4 = 20k\Omega \ \ \text{(Standad Value)} \end{array}$$

4. Select  $R_g$  to meet the desired maximum gain G = 10V/V.

$$\begin{split} G &= 1 + \frac{R_4}{R_3} + \frac{2R_2}{R_g} = 1 + \frac{20 \, k\Omega}{5.1 \, k\Omega} + \frac{2 \times 20 \, k\Omega}{R_g} = 10 \, \text{V} \, / \, \text{V} \\ R_g &= 8 \, k\Omega \rightarrow R_g = 7.87 \, k\Omega \quad (\text{Standard Value}) \end{split}$$

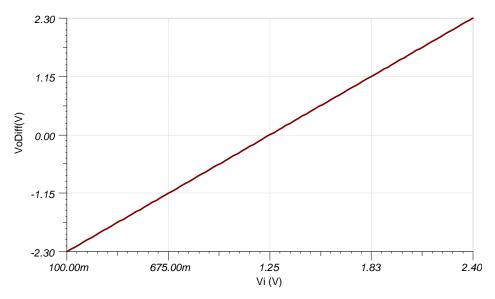

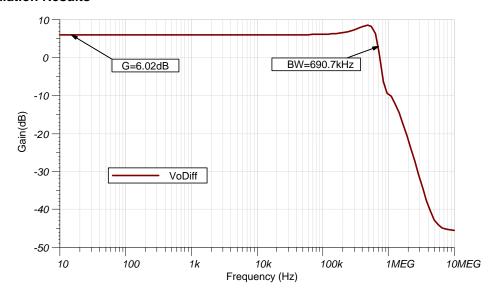

# **Design Simulations**

# **DC Simulation Results**

# **Transient Simulation Results**

## References:

- 1. Analog Engineer's Circuit Cookbooks

- 2. SPICE Simulation File SBOMAU7

- 3. TI Precision Labs

- 4.  $V_{CM}$  vs.  $V_{OUT}$  plots for instrumentation amplifiers with two op amps

- 5. Common-mode Range Calculator for Instrumentation Amplifiers

# **Design Featured Op Amp**

| TLV171                    |                                    |  |  |

|---------------------------|------------------------------------|--|--|

| V <sub>ss</sub>           | 4.5V to 36V                        |  |  |

| V <sub>inCM</sub>         | $(V_{ee}$ –0.1V) to $(V_{cc}$ –2V) |  |  |

| V <sub>out</sub>          | Rail-to-rail                       |  |  |

| V <sub>os</sub>           | 0.25mV                             |  |  |

| I <sub>q</sub>            | 475µA                              |  |  |

| I <sub>b</sub>            | 8pA                                |  |  |

| UGBW                      | 3MHz                               |  |  |

| SR                        | 1.5V/µs                            |  |  |

| #Channels                 | 1,2,4                              |  |  |

| www.ti.com/product/tlv171 |                                    |  |  |

# **Design Alternate Op Amp**

| OPA172                    |                                    |  |  |

|---------------------------|------------------------------------|--|--|

| V <sub>ss</sub>           | 4.5V to 36V                        |  |  |

| V <sub>inCM</sub>         | $(V_{ee}$ –0.1V) to $(V_{cc}$ –2V) |  |  |

| $V_out$                   | Rail-to-rail                       |  |  |

| V <sub>os</sub>           | 0.2mV                              |  |  |

| I <sub>q</sub>            | 1.6mA                              |  |  |

| I <sub>b</sub>            | 8pA                                |  |  |

| UGBW                      | 10MHz                              |  |  |

| SR                        | 10V/µs                             |  |  |

| #Channels                 | 1,2,4                              |  |  |

| www.ti.com/product/opa172 |                                    |  |  |

# Three op amp instrumentation amplifier circuit

# **Design Goals**

| Input V <sub>idit</sub> | Input V <sub>idiff</sub> (V <sub>i2</sub> - V <sub>i1</sub> ) Common-mode Voltage |                 | Output     |            |                 | Supply   |           |

|-------------------------|-----------------------------------------------------------------------------------|-----------------|------------|------------|-----------------|----------|-----------|

| V <sub>i diff Min</sub> | V <sub>i diff Max</sub>                                                           | V <sub>cm</sub> | $V_{oMin}$ | $V_{oMax}$ | V <sub>cc</sub> | $V_{ee}$ | $V_{ref}$ |

| -0.5V                   | +0.5V                                                                             | ±7V             | -5V        | +5V        | +15V            | -15V     | 0V        |

#### **Design Description**

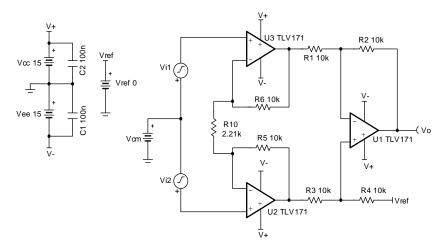

This design uses 3 op amps to build a discrete instrumentation amplifier. The circuit converts a differential signal to a single-ended output signal. Linear operation of an instrumentation amplifier depends upon linear operation of its building block: op amps. An op amp operates linearly when the input and output signals are within the device's input common-mode and output swing ranges, respectively. The supply voltages used to power the op amps define these ranges.

- 1. Use precision resistors to achieve high DC CMRR performance

- 2. R<sub>10</sub> sets the gain of the circuit.

- 3. Add an isolation resistor to the output stage to drive large capacitive loads.

- High-value resistors can degrade the phase margin of the circuit and introduce additional noise in the circuit.

- 5. Linear operation is contingent upon the input common-mode and the output swing ranges of the discrete op amps used. The linear output swing ranges are specified under the A<sub>ol</sub> test conditions in the op amps datasheets.

1. Transfer function of this circuit:

$$\begin{split} V_o &= (V_{i2} - V_{i1}) * G + V_{ref} \\ \text{When } V_{ref} &= 0, \quad \text{the transfer function simplifies to the following equation:} \\ V_o &= (V_{i2} - V_{i1}) * G \\ \text{where } G &= \frac{R_4}{R_3} * 1 + \frac{2 \times R_5}{R_{10}} \end{split}$$

2. Select the feedback loop resistors R<sub>5</sub> and R<sub>6</sub>:

Choose

$$R_5 = R_6 = 10 \text{ k}\Omega$$

(Standard Value)

3. Select  $R_1$ ,  $R_2$ ,  $R_3$ ,  $R_4$ . To set the Vref gain at 1V/V and avoid degrading the instrumentation amplifier's CMRR, ratios of  $R_4/R_3$  and  $R_2/R_1$  must be equal.

Choose

$$R_1 = R_2 = R_3 = R_4 = 10 \text{ k}\Omega$$

(Standard Value)

4. Calculate R<sub>10</sub> to meet the desired gain:

$$\begin{split} G &= \frac{R_4}{R_3} \times (1 + \frac{2^{\times}R_5}{R_{10}}) = 10 \, \frac{V}{V} \qquad \qquad ( ) \\ R_4 &= R_3 = 10 \, k\Omega \\ &\to G = \ 1 + \frac{2^{\times}10 \, k\Omega}{R_{10}} \, = 10 \frac{V}{V} \to \ 1 + \frac{20k\Omega}{R_{10}} \, = 10 \frac{V}{V} \\ &\frac{20 \, k\Omega}{R_{10}} = 9 \frac{V}{V} \to R_{10} = \frac{20k\Omega}{9} = 2222.2 \, \Omega \to R_{10} = 2.21 \, k\Omega \quad \text{(Standard Value)} \end{split}$$

5. To check the common-mode voltage range, download and install the program from reference [5]. Edit the INA\_Data.txt file in the installation directory by adding the code for a 3 op amp INA whose internal amplifiers have the common-mode range, output swing, and supply voltage range as defined by the amplifier of choice (TLV172 in this case). There is no V<sub>be</sub> shift in this design and the gain of the output stage difference amplifeir is 1 V/V. The default supply voltage and reference voltages are ±15 V and 0 V, respectively. Run the program and set the gain and reference voltage accordingly. The resulting V<sub>CM</sub> vs. V<sub>OUT</sub> plot approximates the linear operating region of the discrete INA.

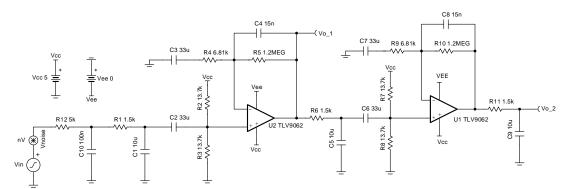

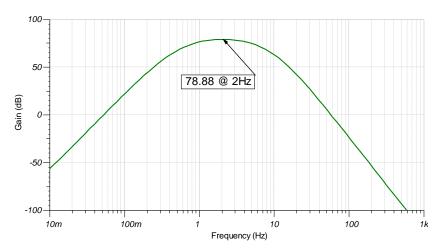

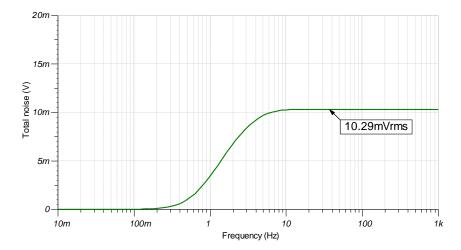

# **Design Simulations**

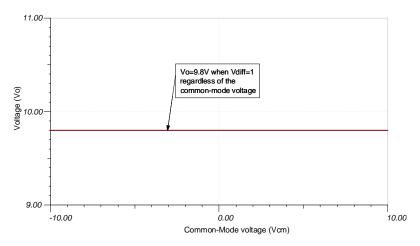

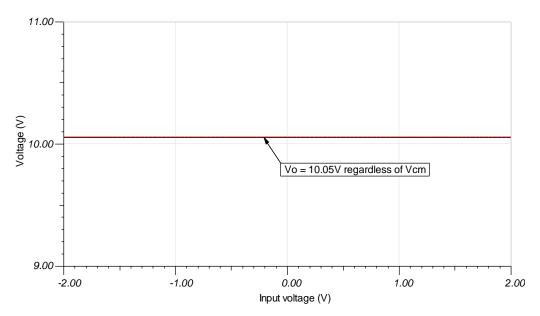

# **DC Simulation Results**

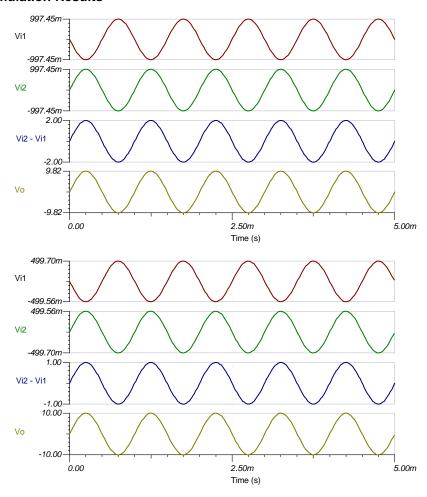

# **Transient Simulation Results**

## References:

- 1. Analog Engineer's Circuit Cookbooks

- 2. SPICE Simulation File SBOMAU8

- 3. TI Precision Labs

- 4. Instrumentation Amplifier  $V_{\text{CM}}$  vs.  $V_{\text{OUT}}$  Plots

- 5. Common-mode Range Calculator for Instrumentation Amplifiers

# **Design Featured Op Amp**

| TLV171                    |                               |  |  |

|---------------------------|-------------------------------|--|--|

| V <sub>ss</sub>           | 4.5V to 36V                   |  |  |

| V <sub>inCM</sub>         | (V−) − 0.1V < Vin < (V+) − 2V |  |  |

| V <sub>out</sub>          | Rail-to-rail                  |  |  |

| V <sub>os</sub>           | 0.25mV                        |  |  |

| I <sub>q</sub>            | 475µA                         |  |  |

| I <sub>b</sub>            | 8pA                           |  |  |

| UGBW                      | 3MHz                          |  |  |

| SR                        | 1.5V/µs                       |  |  |

| #Channels                 | 1,2,4                         |  |  |

| www.ti.com/product/tlv171 |                               |  |  |

# **Design Alternate Op Amp**

|                   | OPA172                           | OPA192                                         |  |

|-------------------|----------------------------------|------------------------------------------------|--|

| V <sub>ss</sub>   | 4.5V to 36V                      | 4.5V to 36V                                    |  |

| V <sub>inCM</sub> | (V–) – 0.1V < Vin <<br>(V+) – 2V | V <sub>ee</sub> -0.1V to V <sub>cc</sub> +0.1V |  |

| V <sub>out</sub>  | Rail-to-rail                     | Rail-to-rail                                   |  |

| V <sub>os</sub>   | 0.2mV                            | ±5µV                                           |  |

| I <sub>q</sub>    | 1.6mA                            | 1mA/Ch                                         |  |

| I <sub>b</sub>    | 8pA                              | 5pA                                            |  |

| UGBW              | 10MHz                            | 10MHz                                          |  |

| SR                | 10V/µs                           | 20V/µs                                         |  |

| #Channels         | 1,2,4                            | 1, 2, 4                                        |  |

|                   | www.ti.com/product/op<br>a172    | www.ti.com/product/op<br>a192                  |  |

SBOA275A-February 2018-Revised January 2019

# Integrator circuit

## **Design Goals**

| Input            |                  | Out              | tput              | Supply            |                 |                 |

|------------------|------------------|------------------|-------------------|-------------------|-----------------|-----------------|

| f <sub>Min</sub> | f <sub>0dB</sub> | f <sub>Max</sub> | V <sub>oMin</sub> | V <sub>oMax</sub> | V <sub>cc</sub> | V <sub>ee</sub> |

| 100Hz            | 1kHz             | 100kHz           | -2.45V            | 2.45V             | 2.5V            | -2.5V           |

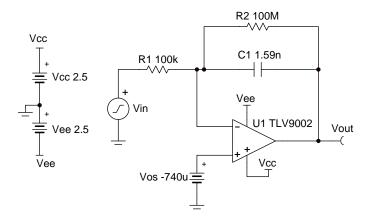

#### **Design Description**

The integrator circuit outputs the integral of the input signal over a frequency range based on the circuit time constant and the bandwidth of the amplifier. The input signal is applied to the inverting input so the output is inverted relative to the polarity of the input signal. The ideal integrator circuit will saturate to the supply rails depending on the polarity of the input offset voltage and requires the addition of a feedback resistor, R<sub>2</sub>, to provide a stable DC operating point. The feedback resistor limits the lower frequency range over which the integration function is performed. This circuit is most commonly used as part of a larger feedback/servo loop which provides the DC feedback path, thus removing the requirement for a feedback resistor.

Copyright © 2018, Texas Instruments Incorporated

- 1. Use as large of a value as practical for the feedback resistor.

- 2. Select a CMOS op amp to minimize the errors from the input bias current.

- 3. The gain bandwidth product (GBP) of the amplifier will set the upper frequency range of the integrator function. The effectiveness of the integration function is usually reduced starting about one decade away from the amplifier bandwidth.

- 4. An adjustable reference needs to be connected to the non-inverting input of the op amp to cancel the input offset voltage or the large DC noise gain will cause the circuit to saturate. Op amps with very low offset voltage may not require this.

The ideal circuit transfer function is given below.

$$V_{out} = -\frac{1}{R_1 \times C_1} \int_0^t V_{in}(t) dt$$

1. Set R<sub>1</sub> to a standard value.

$$R_1 = 100k\Omega$$

2. Calculate C<sub>1</sub> to set the unity-gain integration frequency.

$$C_1 = \frac{1}{2 \times \pi \times R_1 \times f_{0dB}} = \frac{1}{2 \times \pi \times 100 k\Omega \times 1 \text{ kHz}} = 1.59 nF$$

3. Calculate R<sub>2</sub> to set the lower cutoff frequency a decade less than the minimum operating frequency.

$$R_2 \ge \frac{10}{2 \times \pi \times C_1 \times f_{Min}} \ge \frac{10}{2 \times \pi \times 1.59 nF \times 10 Hz} \ge 100 M\Omega$$

4. Select an amplifier with a gain bandwidth at least 10 times the desired maximum operating frequency.

GBP

$$\geq$$

10 × f<sub>Max</sub>  $\geq$  10 × 100kHz  $\geq$  1 MHz

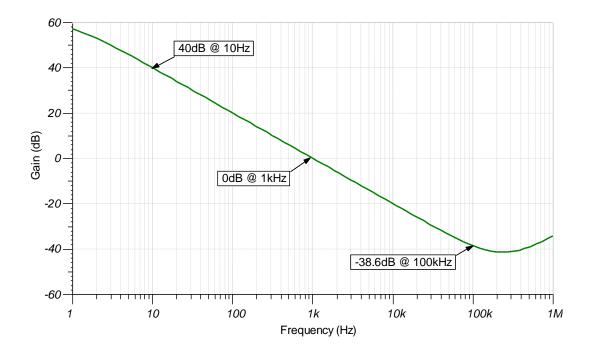

## **Design Simulations**

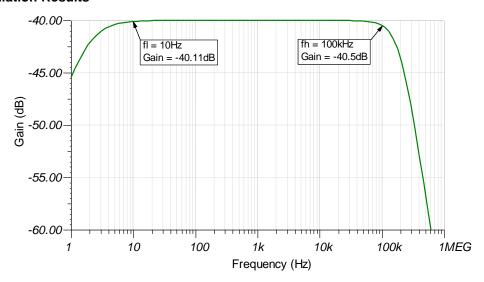

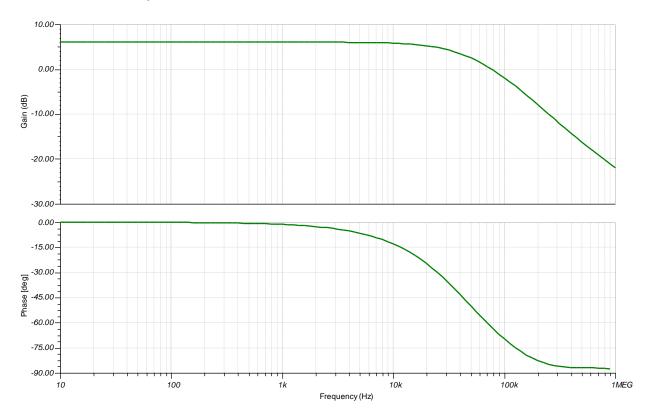

#### **AC Simulation Results**

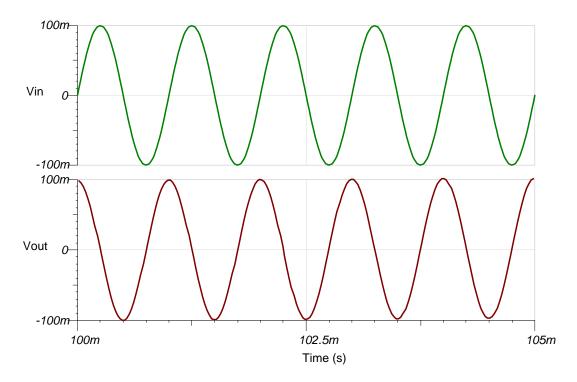

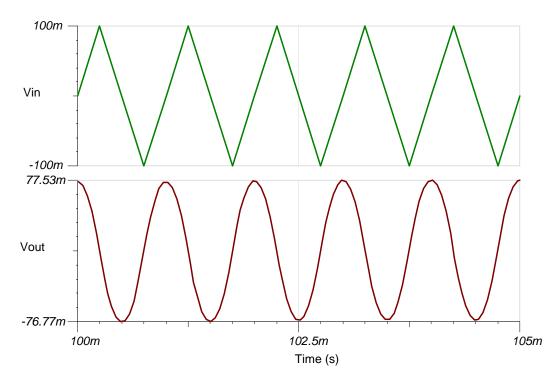

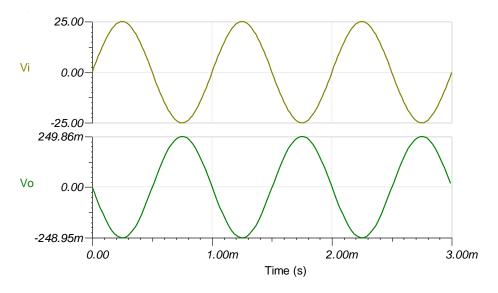

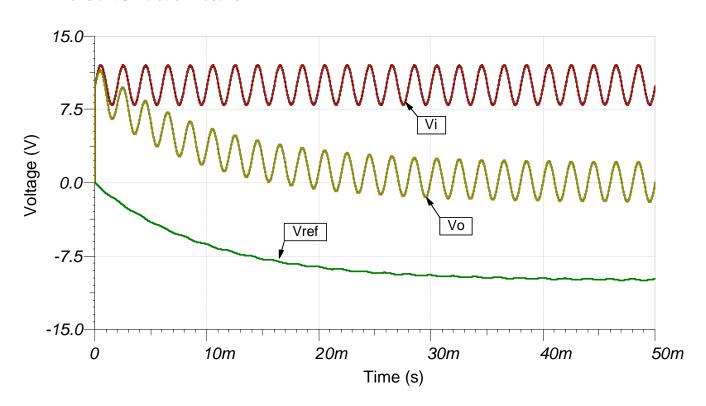

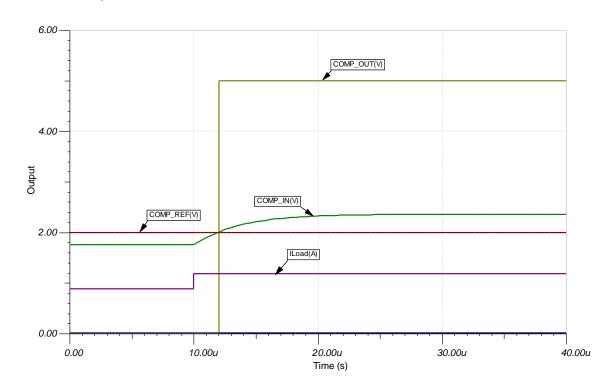

#### **Transient Simulation Results**

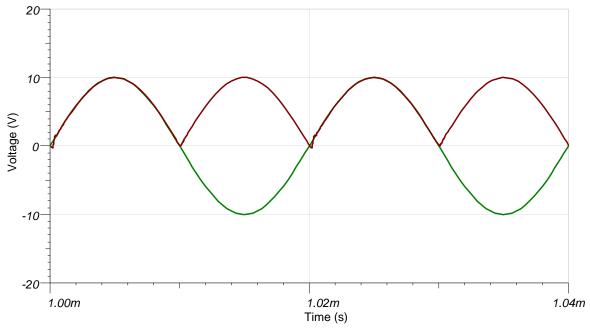

A 1-kHz sine wave input yields a 1-kHz cosine output.

A 1-kHz triangle wave input yields a 1-kHz sine wave output.

www.ti.com

#### **Design References**

See Analog Engineer's Circuit Cookbooks for TI's comprehensive circuit library.

See circuit SPICE simulation file SBOC496.

See TIPD191, www.ti.com/tool/tipd191.

# **Design Featured Op Amp**

| TLV9002                    |                       |  |  |  |

|----------------------------|-----------------------|--|--|--|

| V <sub>cc</sub>            | 1.8V to 5.5V          |  |  |  |

| V <sub>inCM</sub>          | Rail-to-rail          |  |  |  |

| V <sub>out</sub>           | Rail-to-rail<br>0.4mV |  |  |  |

| V <sub>os</sub>            | 0.4mV                 |  |  |  |

| I <sub>q</sub>             | 0.06mA                |  |  |  |

| I <sub>b</sub>             | 5pA                   |  |  |  |

| UGBW                       | 1MHz                  |  |  |  |

| SR                         | 2V/μs                 |  |  |  |

| #Channels                  | 1, 2, 4               |  |  |  |

| www.ti.com/product/tlv9002 |                       |  |  |  |

# **Design Alternate Op Amp**

| OPA376                    |                                      |  |  |  |

|---------------------------|--------------------------------------|--|--|--|

| V <sub>cc</sub>           | 2.2V to 5.5V                         |  |  |  |

| V <sub>inCM</sub>         | $(V_{ee}$ -0.1V) to $(V_{cc}$ -1.3V) |  |  |  |

| $V_{\text{out}}$          |                                      |  |  |  |

| V <sub>os</sub>           | 0.005mV                              |  |  |  |

| I <sub>q</sub>            | 0.76mA                               |  |  |  |

| I <sub>b</sub>            | 0.2pA                                |  |  |  |

| UGBW                      | 5.5MHz                               |  |  |  |

| SR 2V/µs                  |                                      |  |  |  |

| #Channels                 | 1, 2, 4                              |  |  |  |

| www.ti.com/product/opa376 |                                      |  |  |  |

| Revision | Date         | Change                                                                                                   |

|----------|--------------|----------------------------------------------------------------------------------------------------------|

| Α        | January 2019 | Downscale the title and changed title role to 'Amplifiers'. Added link to circuit cookbook landing page. |

SBOA276A-February 2018-Revised January 2019

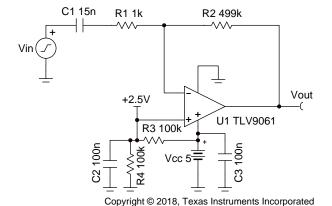

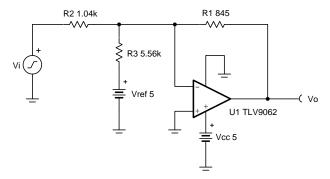

# Differentiator circuit

#### **Design Goals**

| Input            |                  | Out               | tput              | Supply          |                 |                  |

|------------------|------------------|-------------------|-------------------|-----------------|-----------------|------------------|

| f <sub>Min</sub> | f <sub>Max</sub> | V <sub>oMin</sub> | V <sub>oMax</sub> | V <sub>cc</sub> | V <sub>ee</sub> | V <sub>ref</sub> |

| 100Hz            | 5kHz             | 0.1V              | 4.9V              | 5V              | 0V              | 2.5V             |

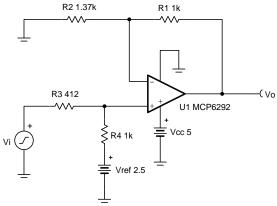

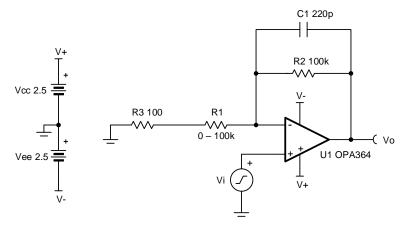

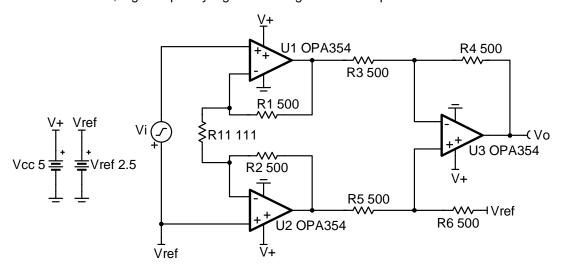

#### **Design Description**

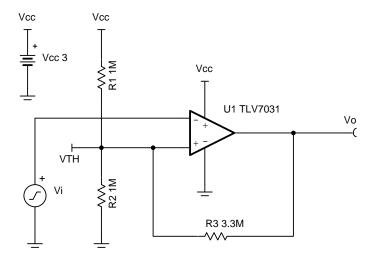

The differentiator circuit outputs the derivative of the input signal over a frequency range based on the circuit time constant and the bandwidth of the amplifier. The input signal is applied to the inverting input so the output is inverted relative to the polarity of the input signal. The ideal differentiator circuit is fundamentally unstable and requires the addition of an input resistor, a feedback capacitor, or both, to be stable. The components required for stability limit the bandwidth over which the differentiator function is performed.

- 1. Select a large resistance for R<sub>2</sub> to keep the value of C<sub>1</sub> reasonable.

- 2. A capacitor can be added in parallel with R2 to filter the high-frequency noise of the circuit. The capacitor will limit the effectiveness of the differentiator function starting about half a decade (approximately 3.5 times) away from the filter cutoff frequency.

- 3. A reference voltage can be applied to the non-inverting input to set the DC output voltage which allows the circuit to work single-supply. The reference voltage can be derived from a voltage divider.

- 4. Operate within the linear output voltage swing (see AoI specification) to minimize non-linearity errors.

The ideal circuit transfer function is given below.

Vout =

$$-R_2 \times C_1 \times \frac{dV_{in}(t)}{dt}$$

1. Set R<sub>2</sub> to a large standard value.

$$R_2 = 499k\Omega$$

2. Set the minimum differentiation frequency at least half a decade below the minimum operating frequency.

$$C_1 \ge \frac{3.5}{2 \times \pi \times R_2 \times f_{min}} \ge \frac{3.5}{2 \times \pi \times 499 k\Omega \times 100 Hz} \ge 11.1$$

nF ≈ 15nF (Standard Value)

3. Set the upper cutoff frequency at least half a decade above the maximum operating frequency.

$$R_1 \leq \frac{1}{3.5 \times 2 \times \pi \times C_1 \times f_{\text{Max}}} \leq \frac{1}{7 \times \pi \times 15 \text{nF} \times 2.5 \text{kHz}} \leq 1 \cdot 2 \text{k}\Omega \approx 1 \quad \text{k}\Omega \quad (Standard \quad Value)$$

4. Calculate the necessary op amp gain bandwidth product (GBP) for the circuit to be stable.

$$\text{GBP} > \tfrac{R_1 + R_2}{2 \times \pi \times R_1^2 \times C_1} > \tfrac{499 k \Omega + 1}{2 \times \pi \times 1} \tfrac{k\Omega}{k\Omega^2 \times 15 nF} > 5 \text{ . 3MHz}$$

- The bandwidth of the TLV9061 is 10MHz, therefore this requirement is met.

- 5. If a feedback capacitor, C<sub>F</sub> , is added in parallel with R<sub>2</sub>, the equation to calculate the cutoff frequency follows.

$$f_c = \frac{1}{2 \times \pi \times R_2 \times C_F}$$

6. Calculate the resistor divider values for a 2.5-V reference voltage.

$$R_3 = \frac{V_{cc} - V_{ref}}{V_{ref}} \times R_4 = \frac{5V - 2.5V}{2.5V} \times R_4 = R_4$$

$$R_3 = R_4 = 100 k\Omega \ \ (Standard \ \ Values)$$

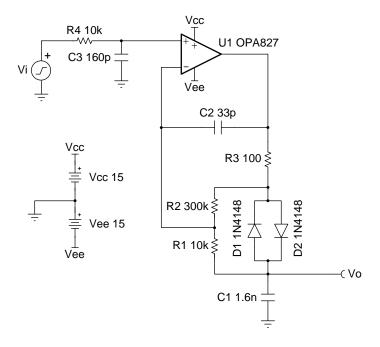

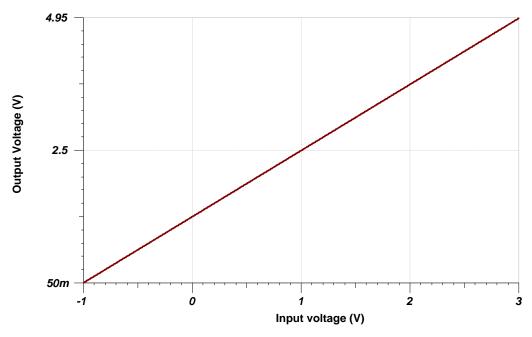

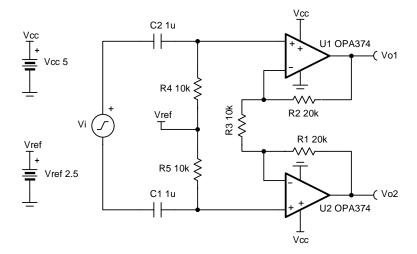

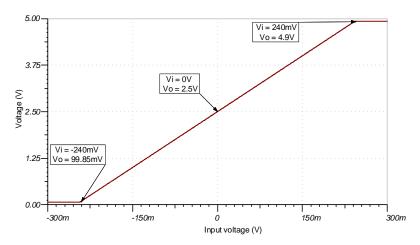

# **Design Simulations**

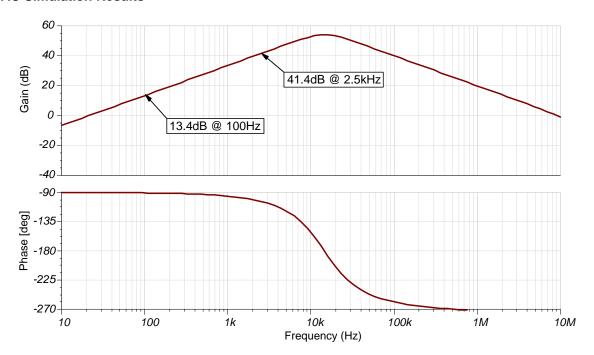

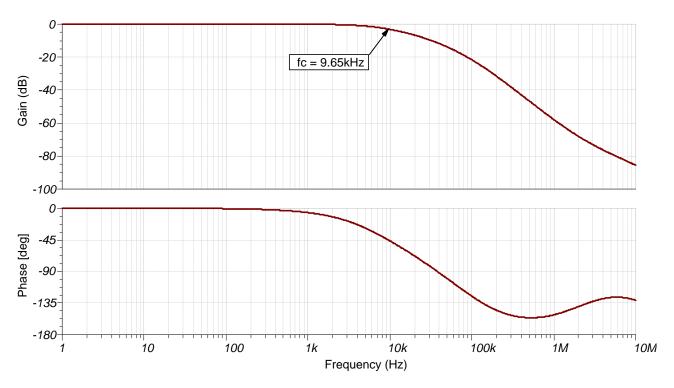

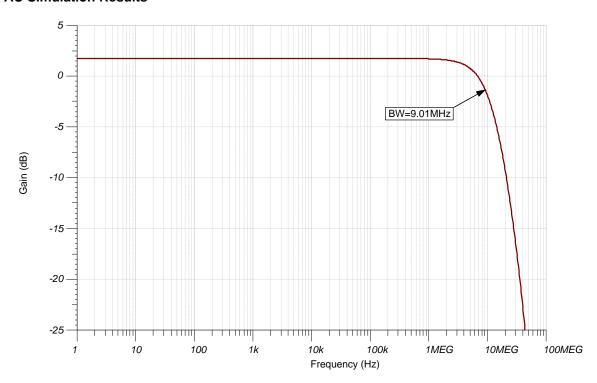

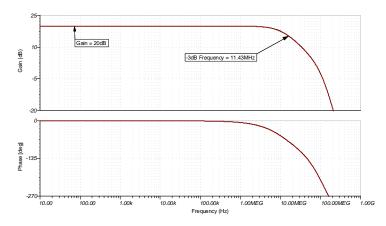

# **AC Simulation Results**

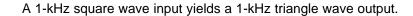

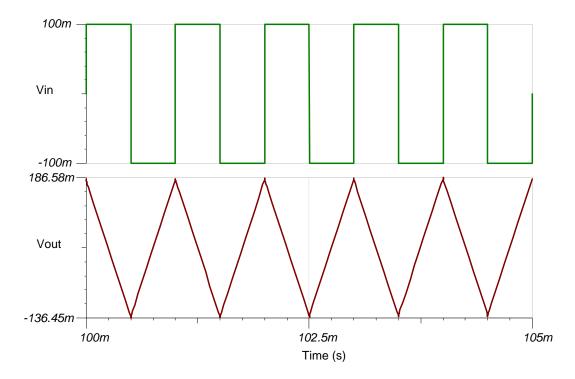

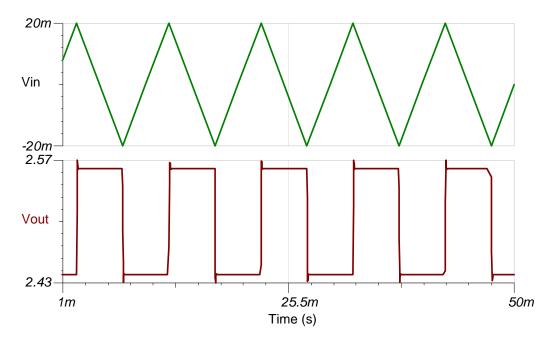

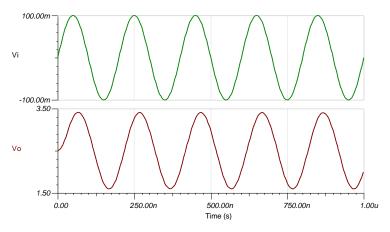

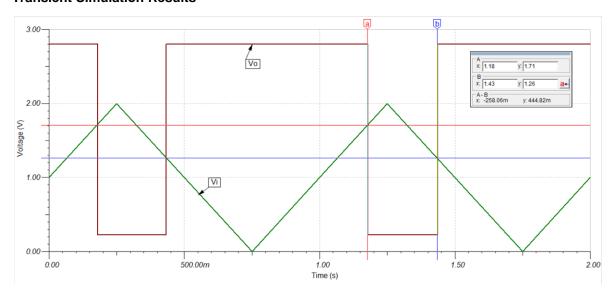

#### **Transient Simulation Results**

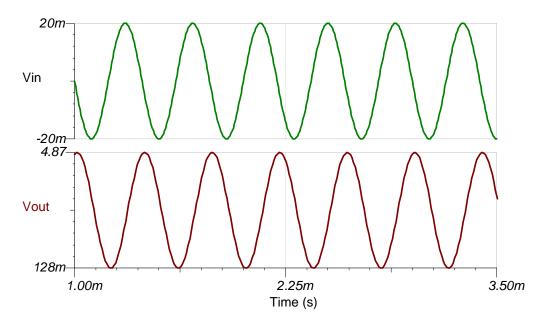

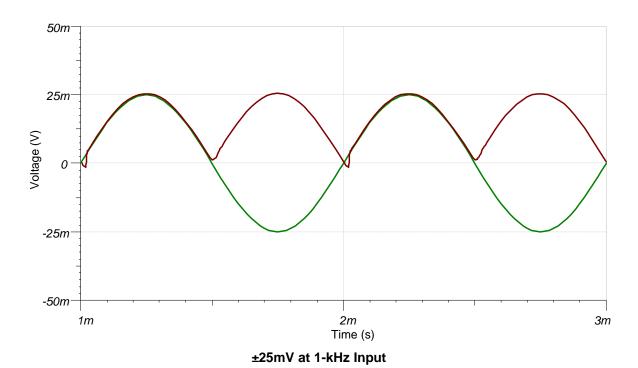

A 2.5-kHz sine wave input yields a 2.5-kHz cosine output.

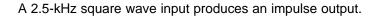

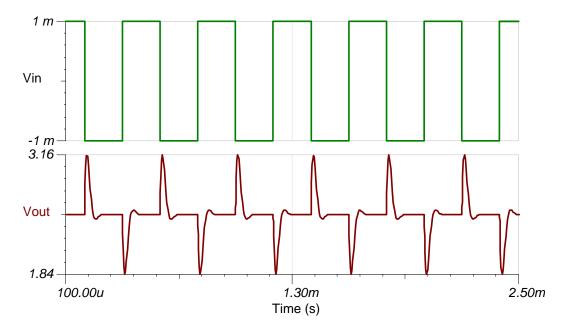

# A 100-Hz triangle wave input yields a square wave output.

www.ti.com

# **Design Featured Op Amp**

See Analog Engineer's Circuit Cookbooks for TI's comprehensive circuit library. See circuit SPICE simulation file SBOC497.

| TLV9061                    |                       |  |  |

|----------------------------|-----------------------|--|--|

| V <sub>cc</sub>            | 1.8V to 5.5V          |  |  |

| V <sub>inCM</sub>          | Rail-to-rail          |  |  |

| V <sub>out</sub>           | Rail-to-rail<br>0.3mV |  |  |

| V <sub>os</sub>            |                       |  |  |

| I <sub>q</sub>             | 0.538mA               |  |  |

| I <sub>b</sub>             | 0.5pA                 |  |  |

| UGBW                       | 10MHz                 |  |  |

| SR                         | 6.5V/µs               |  |  |

| #Channels                  | 1, 2, 4               |  |  |

| www.ti.com/product/tlv9061 |                       |  |  |

# **Design Alternate Op Amp**

| OPA374                    |                     |  |  |  |

|---------------------------|---------------------|--|--|--|

| V <sub>cc</sub>           | 2.3V to 5V          |  |  |  |

| V <sub>inCM</sub>         | Rail-to-rail        |  |  |  |

| V <sub>out</sub>          | Rail-to-rail<br>1mV |  |  |  |

| V <sub>os</sub>           |                     |  |  |  |

| I <sub>q</sub>            | 0.585mA             |  |  |  |

| I <sub>b</sub>            | 0.5pA               |  |  |  |

| UGBW                      | 6.5MHz              |  |  |  |

| SR                        | 0.4V/µs             |  |  |  |

| #Channels                 | 1, 2, 4             |  |  |  |

| www.ti.com/product/opa374 |                     |  |  |  |

| Revision | Date         | Change                                                                                                   |

|----------|--------------|----------------------------------------------------------------------------------------------------------|

| А        | January 2019 | Downscale the title and changed title role to 'Amplifiers'. Added link to circuit cookbook landing page. |

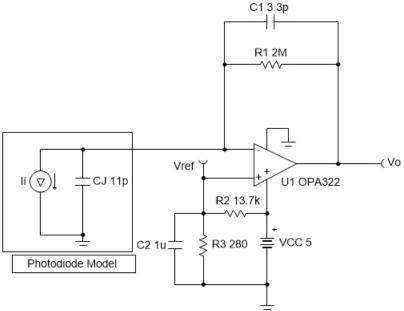

# Transimpedance amplifier circuit

#### **Design Goals**

| Input             |                   | Output     |            | BW             | Supply          |                 |

|-------------------|-------------------|------------|------------|----------------|-----------------|-----------------|

| l <sub>iMin</sub> | I <sub>iMax</sub> | $V_{oMin}$ | $V_{oMax}$ | f <sub>p</sub> | V <sub>cc</sub> | V <sub>ee</sub> |

| 0A                | 50µA              | 0V         | 5V         | 10kHz          | 15V             | -15V            |

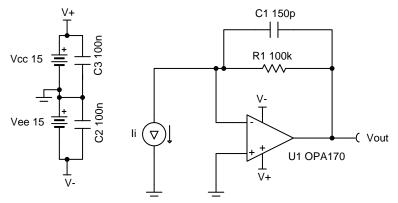

#### **Design Description**

The transimpedance op amp circuit configuration converts an input current source into an output voltage. The current to voltage gain is based on the feedback resistance. The circuit is able to maintain a constant voltage bias across the input source as the input current changes which benefits many sensors.

Copyright © 2018, Texas Instruments Incorporated

- 1. Use a JFET or CMOS input op amp with low bias current to reduce DC errors.

- 2. A bias voltage can be added to the non-inverting input to set the output voltage for 0-A input currents.

- 3. Operate within the linear output voltage swing (see A<sub>ol</sub> specification) to minimize non-linearity errors.

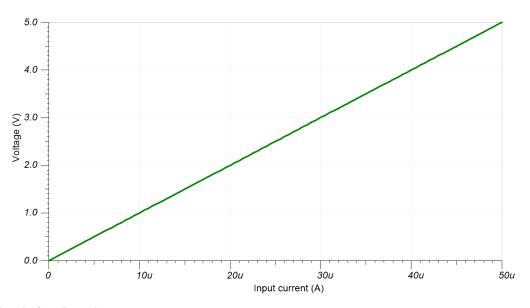

1. Select the gain resistor.

$$R_1 = \frac{V_{oMax} - V_{oMin}}{I_{iMax}} = \frac{5V - 0V}{50\mu A} = 100k\Omega$$

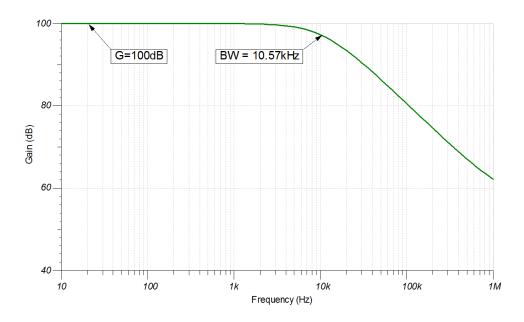

2. Select the feedback capacitor to meet the circuit bandwidth.

$$C_1 \le \frac{1}{2 \times \pi \times R_1 \times f_p}$$

$$C_1 \le \frac{1}{2 \times \pi \times 100 \text{k}\Omega \times 10 \text{kHz}} \le 159 \text{pF} \approx 150 \text{pF} \text{ (Standard Value)}$$

3. Calculate the necessary op amp gain bandwidth (GBW) for the circuit to be stable.

$$GBW > \frac{C_i + C_1}{2 \times \pi \times R_1 \times C_1^{-2}} > \frac{6pF + 150pF}{2 \times \pi \times 100k\Omega \times (150pF)^2} > 11.03kHz$$

where

$$C_i = C_s + C_d + C_{cm} = 0pF + 3pF + 3pF = 6pF$$

given

- C<sub>s</sub>: Input source capacitance

- C<sub>d</sub>: Differential input capacitance of the amplifier

- C<sub>cm</sub>: Common-mode input capacitance of the inverting input

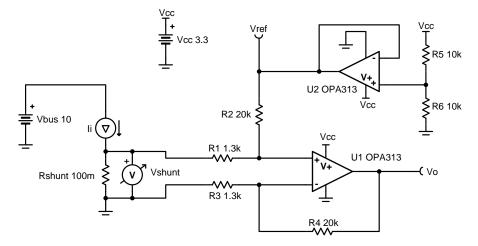

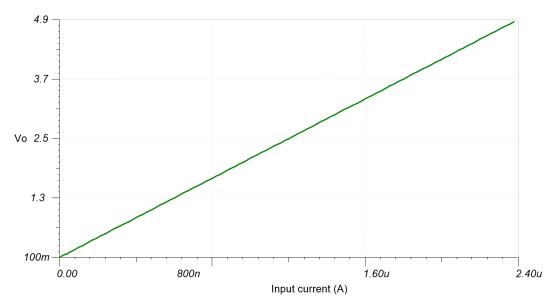

# **Design Simulations**

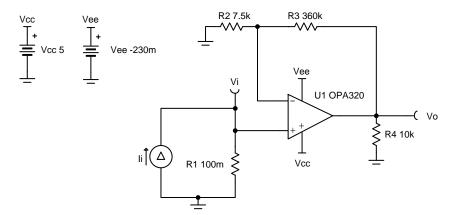

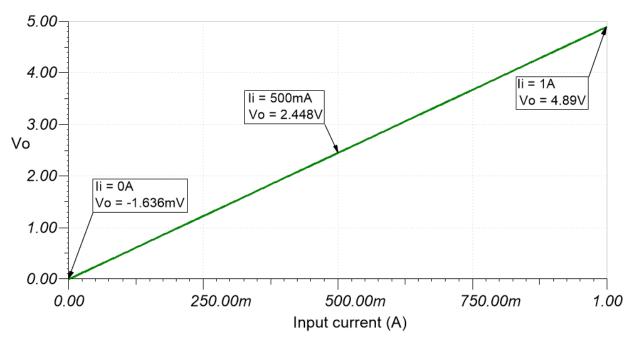

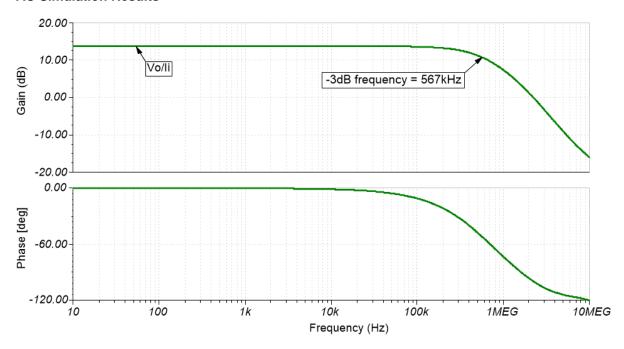

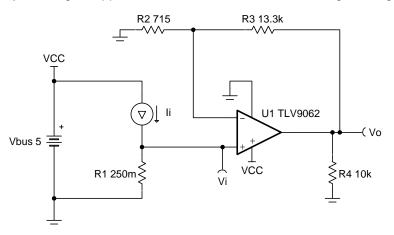

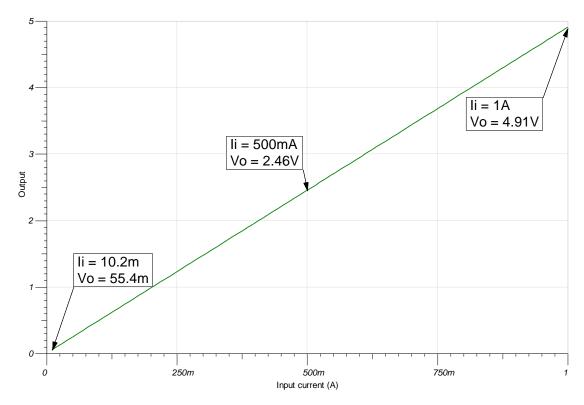

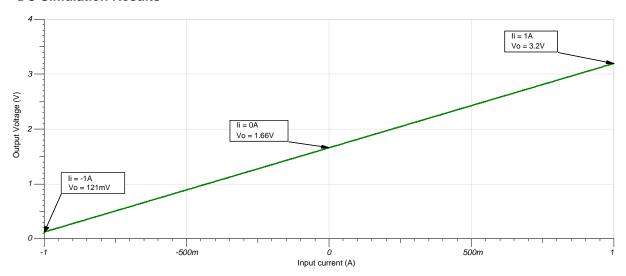

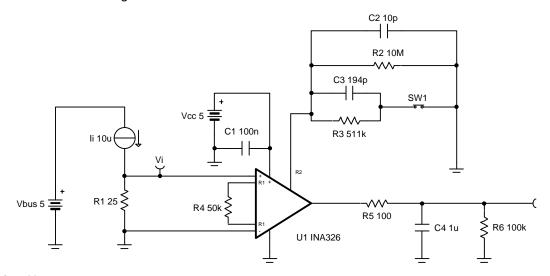

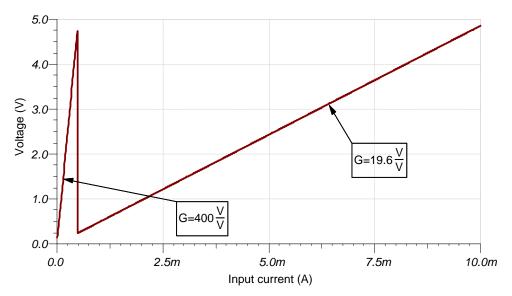

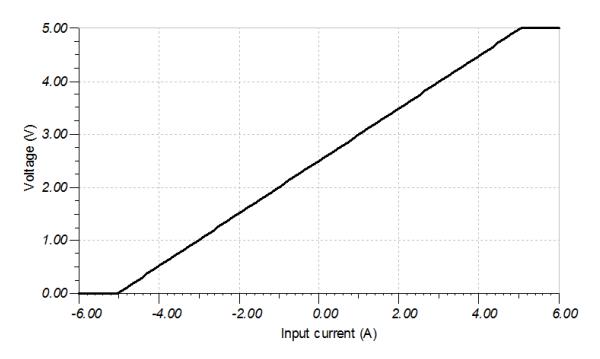

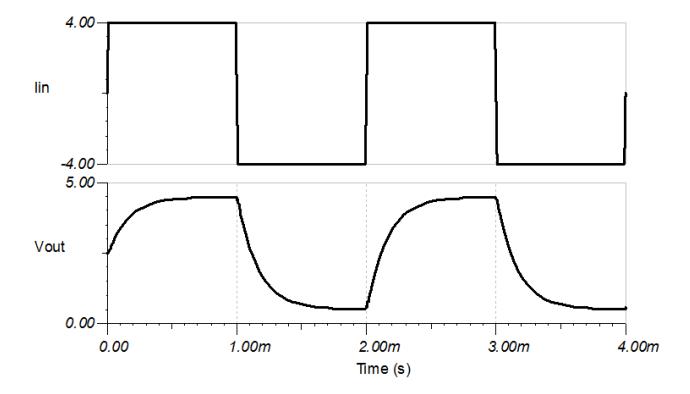

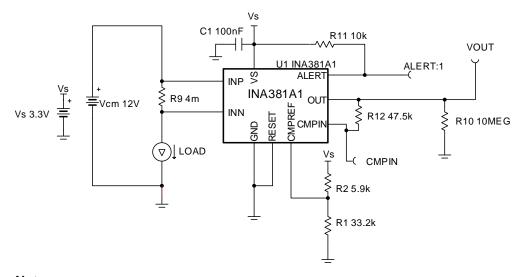

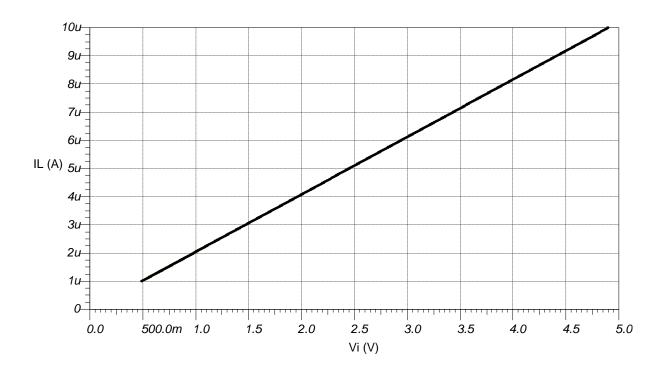

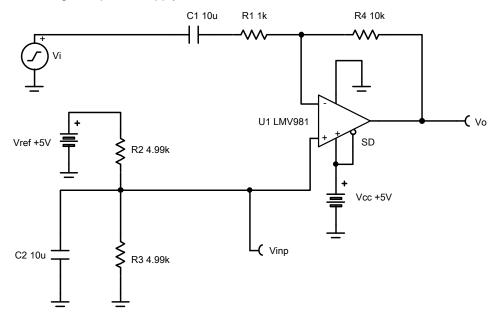

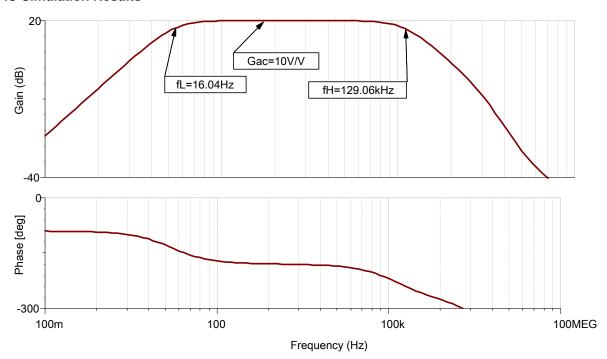

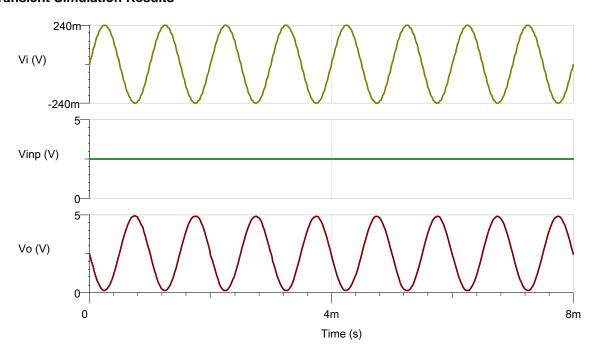

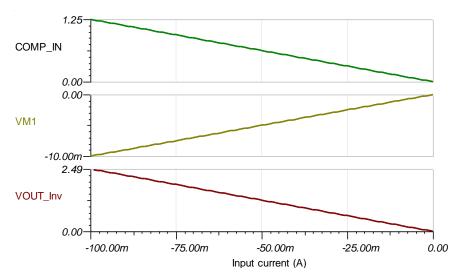

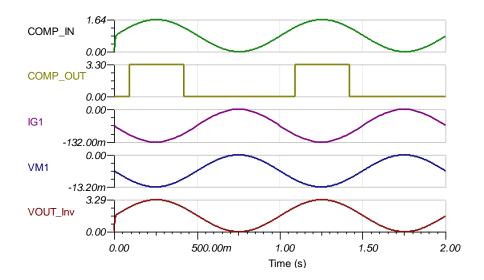

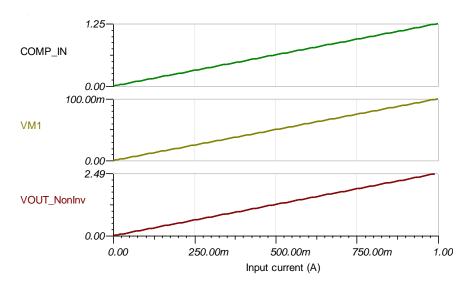

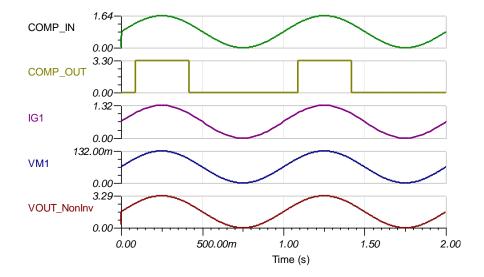

# **DC Simulation Results**

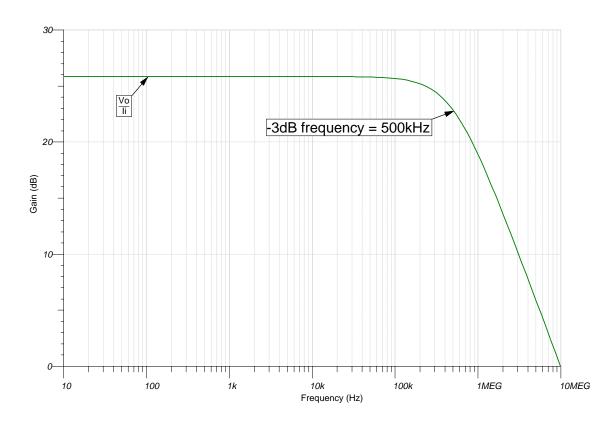

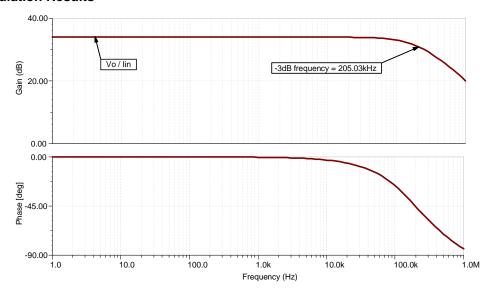

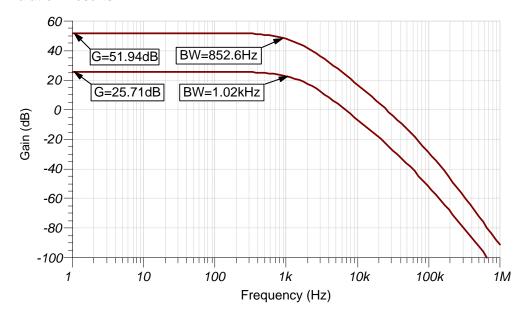

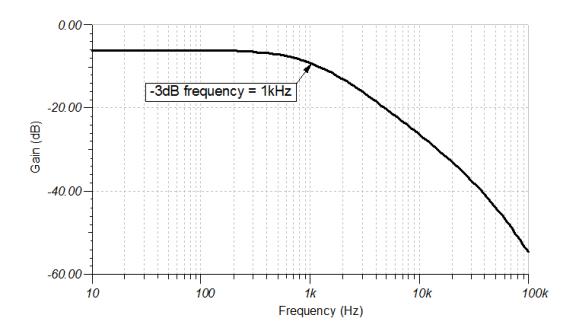

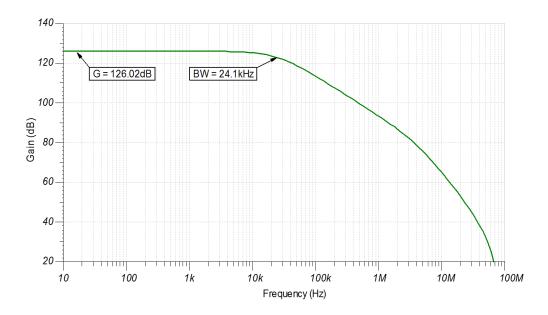

# **AC Simulation Results**

# **Design References**

See Analog Engineer's Circuit Cookbooks for TI's comprehensive circuit library.

See circuit SPICE simulation file SBOC501.

See TIPD176, www.ti.com/tool/tipd176.

# **Design Featured Op Amp**

| OPA170                    |                                    |  |  |  |

|---------------------------|------------------------------------|--|--|--|

| V <sub>cc</sub>           | 2.7V to 36V                        |  |  |  |

| V <sub>inCM</sub>         | $(V_{ee}$ –0.1V) to $(V_{cc}$ –2V) |  |  |  |

| V <sub>out</sub>          | Rail-to-rail                       |  |  |  |

| V <sub>os</sub>           | 0.25mV                             |  |  |  |

| I <sub>q</sub>            | 0.11mA                             |  |  |  |

| I <sub>b</sub>            | 8pA                                |  |  |  |

| UGBW                      | 1.2MHz                             |  |  |  |

| SR                        | 0.4V/µs                            |  |  |  |

| #Channels                 | 1, 2, 4                            |  |  |  |

| www.ti.com/product/opa170 |                                    |  |  |  |

# **Design Alternate Op Amp**

| OPA1671                    |                                                    |  |  |  |

|----------------------------|----------------------------------------------------|--|--|--|

| V <sub>cc</sub>            | 1.7V to 5.5V                                       |  |  |  |

| V <sub>inCM</sub>          | Rail-to-rail                                       |  |  |  |

| V <sub>out</sub>           | $(V_{ee}$ +10mV) to $(V_{cc}$ -10mV) @ 275 $\mu$ A |  |  |  |

| V <sub>os</sub>            | 250µV                                              |  |  |  |

| I <sub>q</sub>             | 940µA                                              |  |  |  |

| I <sub>b</sub>             | 1pA                                                |  |  |  |

| UGBW                       | 12MHz                                              |  |  |  |

| SR                         | 5V/μs                                              |  |  |  |

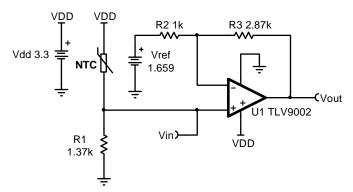

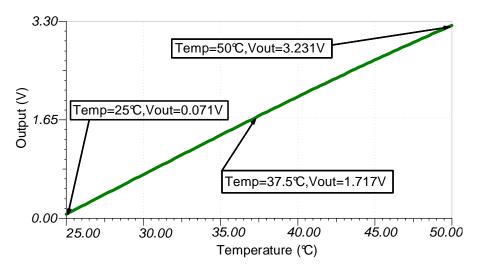

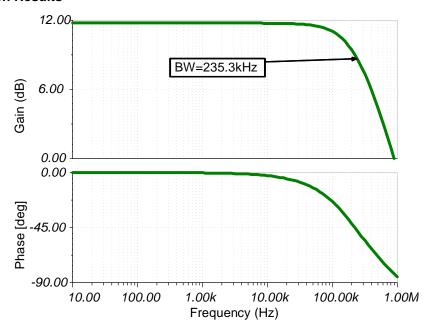

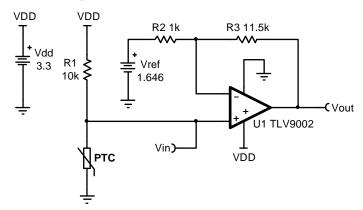

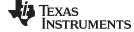

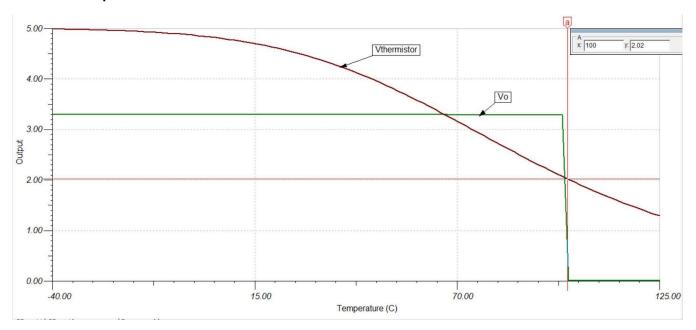

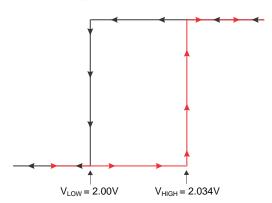

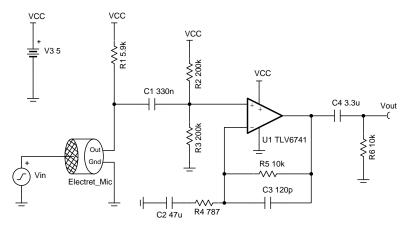

| #Channels                  | 1                                                  |  |  |  |